Multiplication Section

3-5

Central Processing Unit

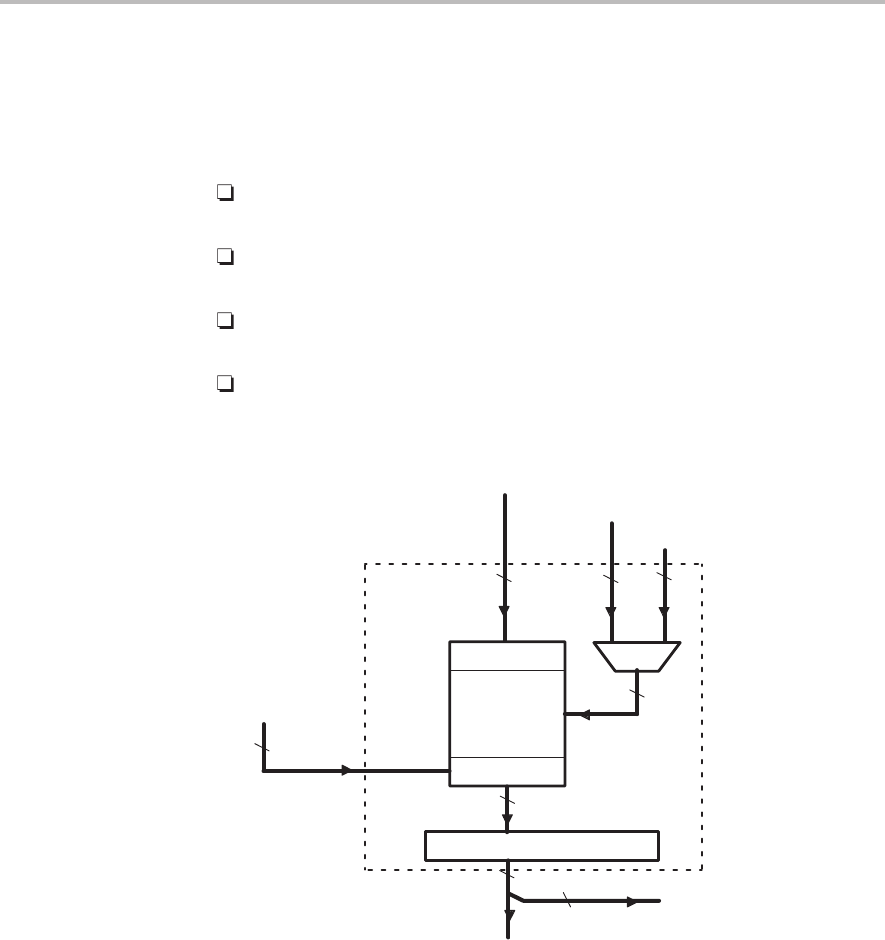

3.2 Multiplication Section

The ’C2xx uses a 16-bit × 16-bit hardware multiplier that can produce a signed

or unsigned 32-bit product in a single machine cycle. As shown in Figure 3–5,

the multiplication section consists of:

The 16-bit temporary register (TREG), which holds one of the multipli-

cands

The multiplier, which multiplies the TREG value by a second value from

data memory or program memory

The 32-bit product register (PREG), which receives the result of the multi-

plication

The product shifter, which scales the PREG value before passing it to the

CALU.

Figure 3–5. Block Diagram of the Multiplication Section

32

MUX

PREG

Multiplier

16 × 16

16

TREG

Product shifter (32 bits)

Multiplication

section

From data memory

16

From data

memory

16

From program memory

16

To CALU

32

From data memory

16

16

To data memory

To high word

of PREG

3.2.1 Multiplier

The 16-bit × 16-bit hardware multiplier can produce a signed or unsigned

32-bit product in a single machine cycle. The two numbers being multiplied are

treated as 2s-complement numbers, except during unsigned multiplication

(MPYU instruction). Descriptions of the inputs and output of the multiplier fol-

low.