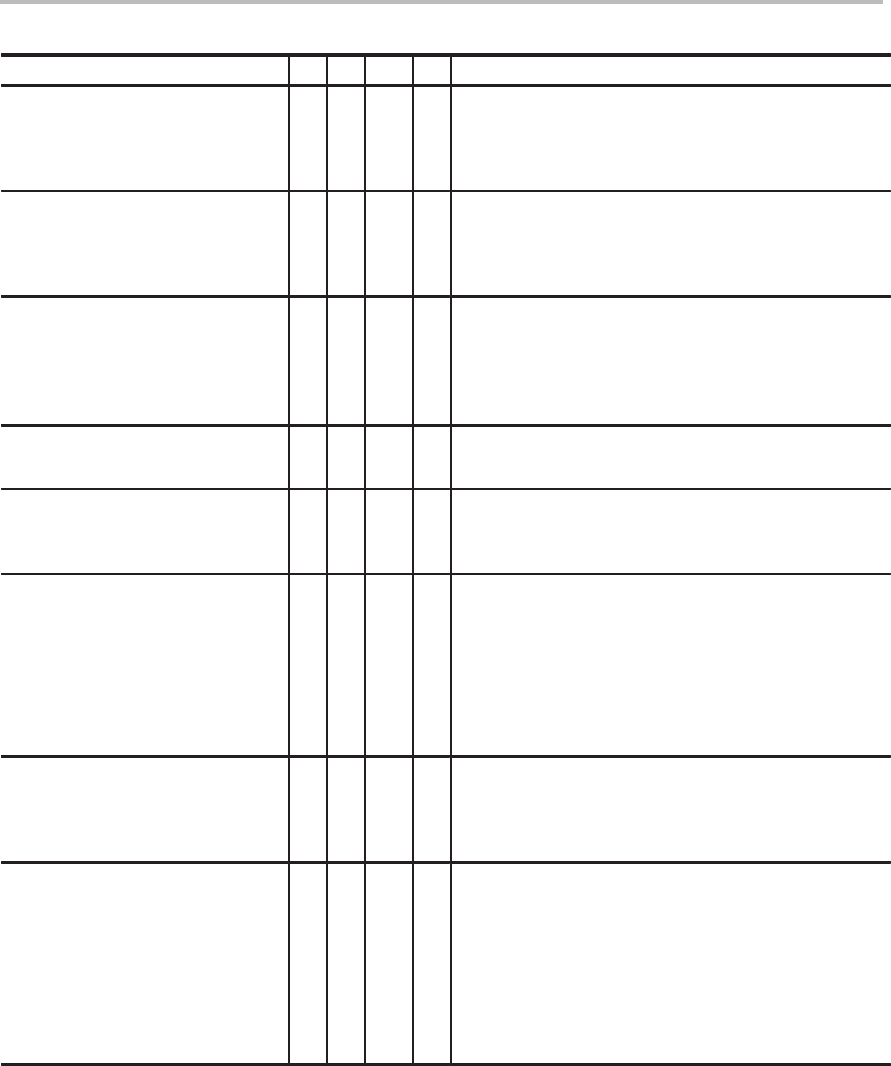

Instruction Set Comparison Table

B-26

Syntax

Description5x2xx2x1x

POPD

dma

POPD {

ind

} [

, next ARP

]

√

√

√

√

√

√

Pop Top of Stack to Data Memory

Transfer the value on the top of the stack into the ad-

dressed data-memory location and then pop the stack

one level.

PSHD

dma

PSHD {

ind

} [

, next ARP

]

√

√

√

√

√

√

Push Data-Memory Value Onto Stack

Copy the addressed data-memory location onto the

top of the stack. The stack is pushed down one level

before the value is copied.

PUSH

√ √ √ √

Push Low Accumulator Onto Stack

Copy the contents of the 12 (TMS320C1x) or 16

(TMS320C2x/2xx/5x) LSBs of the accumulator onto

the top of the hardware stack. The stack is pushed

down one level before the value is copied.

RC

√ √ √

Reset Carry Bit

Reset the C status bit to 0.

RET

√ √ √

Return From Subroutine

Copy the contents of the top of the stack into the PC

and pop the stack one level.

RET[

D

]

√

Return From Subroutine With Optional Delay

Copy the contents of the top of the stack into the PC

and pop the stack one level.

If you specify a delayed branch (RETD), the next two

instruction words (two 1-word instructions or one

2-word instruction) are fetched and executed before

the return.

RETC

cond

1

[

, cond

2

] [, ...]

√

Return Conditionally

If the specified conditions are met, RETC performs a

standard return. Not all combinations of conditions are

meaningful.

RETC[

D

]

cond

1

[

, cond

2

] [, ...]

√

Return Conditionally With Optional Delay

If the specified conditions are met, RETC performs a

standard return. Not all combinations of conditions are

meaningful.

If you specify a delayed branch (RETCD), the next two

instruction words (two 1-word instructions or one

2-word instruction) are fetched and executed before

the return.