’C209 On-Chip Peripherals

11-15

TMS320C209

Table 11–5. ’C209 Input Clock Modes

Clock Mode CLKOUT1 Rate CLKMOD Oscillator PLL

÷ 2 CLKOUT1 = CLKIN ÷ 2 0 Enabled Disabled

× 2 CLKOUT1 = CLKIN × 2 1 Disabled Enabled

Remember the following points when configuring the clock mode:

The modes cannot be configured dynamically. After you change the level

on CLKMOD, the mode is not changed until a hardware reset is executed

(RS

low or RS high).

The clock doubler mode uses an internal phase-locked loop (PLL) that re-

quires approximately 2200 cycles to lock. Delay the rising edge of RS

(or

the falling edge of RS) until at least three cycles after the PLL has stabi-

lized. When the PLL is used, the duty cycle of the CLKIN signal is more

flexible, but the minimum duty cycle should not be less than 10 nanosec-

onds. When the PLL is not used, no phase-locking time is necessary, but

the minimum pulse width must be 45% of the minimum clock cycle.

11.4.2 ’C209 Timer Control Register (TCR)

Figure 11–4 shows the bit fields of the ’C209 TCR, and descriptions of the bit

fields follow the figure.

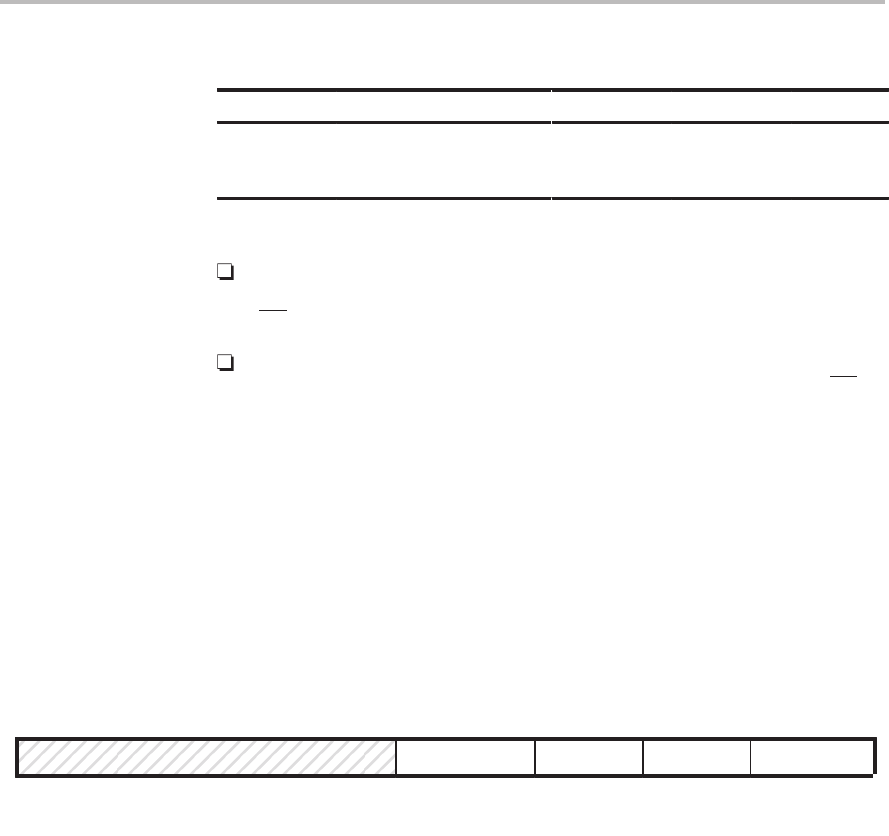

Figure 11–4.’C209 Timer Control Register (TCR) — I/O Address FFFCh

15–10 9–6 5 4 3–0

Reserved PSC TRB TSS TDDR

0 R/W–0 R/W–0 W–0 R/W–0

Note: Note: 0 = Always read as zeros; R = Read access; W = Write access; value following dash (–) is value after reset.

Bits 15–10 Reserved. TCR bits 10–15 are reserved and are always read as 0s.

Bits 9–6 PSC — Timer prescaler counter. These four bits hold the current prescale count for

the timer. For every CLKOUT1 cycle that the PSC value is greater than 0, the PSC

decrements by one. One CLKOUT1 cycle after the PSC reaches 0, the PSC is loaded

with the contents of the TDDR, and the timer counter register (TIM) decrements by

one. The PSC is also reloaded whenever the timer reload bit (TRB) is set by software.

The PSC can be checked by reading the TCR, but it cannot be set directly. It must get

its value from the timer divide-down register (TDDR). At reset, the PSC is set to 0.

Bit 5 TRB — Timer reload bit. When you write a 1 to TRB, the TIM is loaded with the value

in the PRD, and the prescaler counter (PSC) is loaded with the value in the timer di-

vide-down register (TDDR). The TRB bit is always read as zero.