MPYU

Multiply Unsigned

7-120

Syntax MPYU

dma

Direct addressing

MPYU

ind

[, AR

n

] Indirect addressing

Operands dma: 7 LSBs of the data-memory address

n: Value from 0 to 7 designating the next auxiliary register

ind: Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

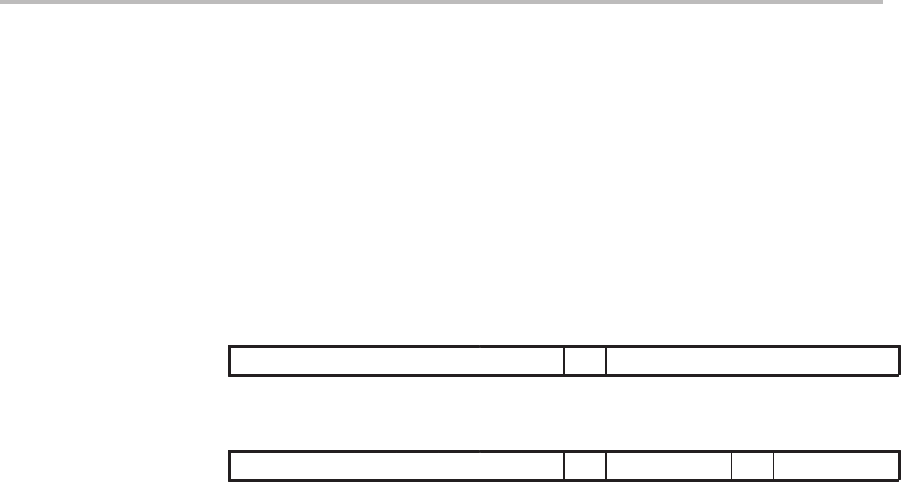

MPYU

dma

1514131211109876543210

0

10101010 dma

MPYU

ind

[,AR

n

]

1514131211109876543210

0

10101011 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

Execution Increment PC, then ...

Unsigned (TREG) × unsigned (data-memory address) → PREG

Status Bits None

This instruction is not affected by SXM.

Description The unsigned contents of TREG are multiplied by the unsigned contents of the

addressed data-memory location. The result is placed in the product register

(PREG). The multiplier acts as a signed 17 × 17-bit multiplier for this instruc-

tion, with the MSB of both operands forced to 0.

When another instruction passes the resulting PREG value to data memory

or to the CALU, the value passes first through the product shifter at the output

of the PREG. This shifter always invokes sign extension on the PREG value

when PM = 3 (right-shift-by-6 mode). Therefore, this shift mode should not be

used if unsigned products are desired.

The MPYU instruction is particularly useful for computing multiple-precision

products, such as when multiplying two 32-bit numbers to yield a 64-bit prod-

uct.

Words 1

Opcode