Load TREG and Accumulate Previous Product

LTA

7-93

Assembly Language Instructions

Syntax LTA

dma

Direct addressing

LTA

ind

[, AR

n

] Indirect addressing

Operands dma: 7 LSBs of the data-memory address

n: Value from 0 to 7 designating the next auxiliary register

ind: Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

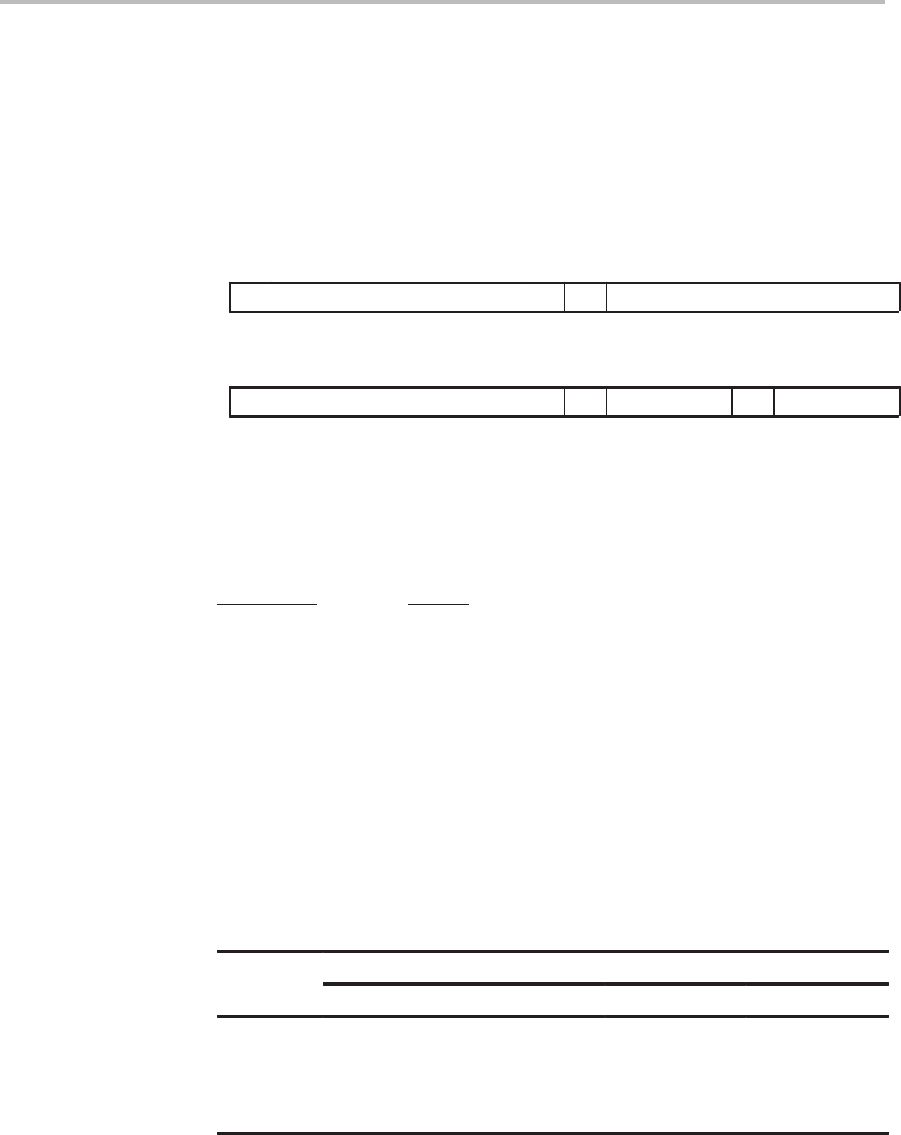

LTA

dma

1514131211109876543210

0

11100000 dma

LTA

ind

[, AR

n

]

1514131211109876543210

0

11100001 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

Execution Increment PC, then ...

(data-memory address) → TREG

(ACC) + shifted (PREG) → ACC

Status Bits

Affected by Affects

PM and OVM C and OV

Description TREG is loaded with the contents of the specified data-memory address. The

contents of the product register, shifted as defined by the PM status bits, are

added to the accumulator, and the result is placed in the accumulator.

The carry bit is set (C = 1) if the result of the addition generates a carry and

is cleared (C = 0) if it does not generate a carry.

The function of the LTA instruction is a subtask of the LTD instruction.

Words 1

Cycles for a Single LTA Instruction

Program

Operand ROM DARAM SARAM External

DARAM 1 1 1 1+p

SARAM 1 1 1, 2

†

1+p

External 1+d 1+d 1+d 2+d+p

†

If the operand and the code are in the same SARAM block

Opcode

Cycles