CLKOUT1-Pin Control (CLK) Register

8-7

On-Chip Peripherals

8.3 CLKOUT1-Pin Control (CLK) Register

You can use bit 0 of the CLK register to turn off the pin for the master clock out-

put signal (CLKOUT1). The CLK register is located at address FFE8h in I/O

space and has the organization shown in Figure 8–3.

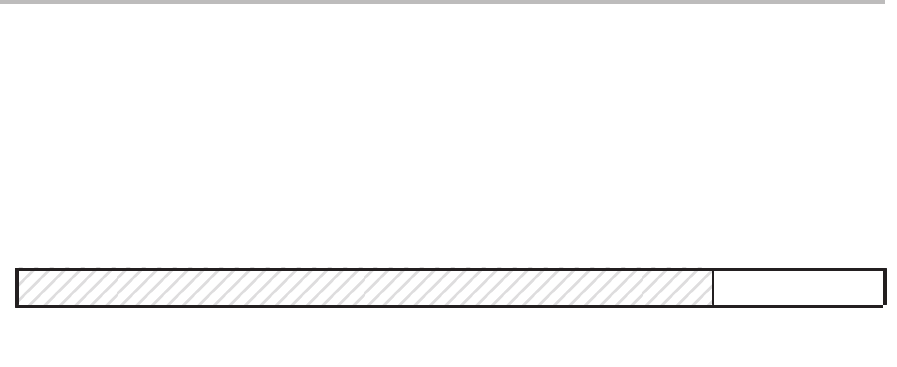

Figure 8–3. ’C2xx CLK Register — I/O-Space Address FFE8h

15 1 0

Reserved CLKOUT1

0 R/W–0

Note: 0 = Always read as zeros; R = Read access; W = Write access; value following dash (–) is value after reset.

If the CLKOUT1 bit is 1, the CLKOUT1 signal is not available at the CLKOUT1

pin; if the bit is 0, CLKOUT1 is available at the pin. At reset, this bit is cleared

to 0. When the IDLE instruction puts the CPU into a power-down mode,

CLKOUT1 remains active at the pin if the CLKOUT1 bit is 0. (For more informa-

tion on the ’C2xx power-down mode, see section 5.8,

Power-Down Mode

, on

page 5-36).

For the current status of CLKOUT1, read bit 0. To change the status, write to

bit 0. When programming, allow the CLKOUT1 pin two cycles to change its

state from on to off or from off to on. Bits 15–1 are reserved and are always

read as 0s.