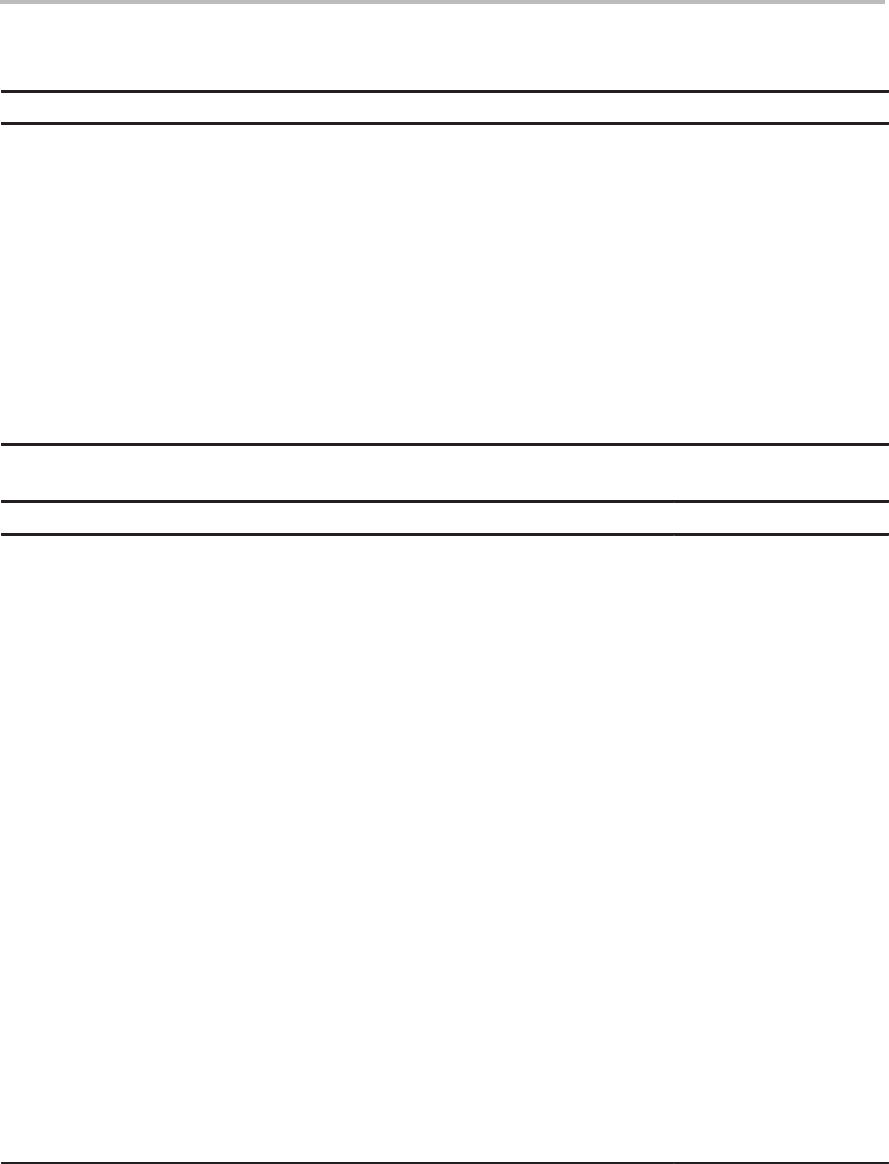

Instruction Set Summary

7-9

Assembly Language Instructions

Table 7–4. Branch Instructions (Continued)

Mnemonic OpcodeCyclesWordsDescription

CALL Call subroutine, indirect 2 4 0111 1010 1AAA AAAA

+ 1 word

CC Call conditionally 2 4 (conditions true)

2 (any condition false)

1110 10TP ZLVC ZLVC

+ 1 word

INTR Soft interrupt 1 4 1011 1110 011I NTR#

NMI Nonmaskable interrupt 1 4 1011 1110 0101 0010

RET Return from subroutine 1 4 1110 1111 0000 0000

RETC Return conditionally 1 4 (conditions true)

2 (any condition false)

1110 11TP ZLVC ZLVC

TRAP Software interrupt 1 4 1011 1110 0101 0001

Table 7–5. Control Instructions

Mnemonic Description Words Cycles Opcode

BIT Test bit, direct or indirect 1 1 0100 BITX IAAA AAAA

BITT Test bit specified by TREG, direct or indirect 1 1 0110 1111 IAAA AAAA

CLRC Clear C bit 1 1 1011 1110 0100 1110

Clear CNF bit 1 1 1011 1110 0100 0100

Clear INTM bit 1 1 1011 1110 0100 0000

Clear OVM bit 1 1 1011 1110 0100 0010

Clear SXM bit 1 1 1011 1110 0100 0110

Clear TC bit 1 1 1011 1110 0100 1010

Clear XF bit 1 1 1011 1110 0100 1100

IDLE Idle until interrupt 1 1 1011 1110 0010 0010

LDP

Load data page pointer,

direct or indirect

1 2 0000 1101 IAAA AAAA

Load data page pointer,

short immediate

1 2 1011 110I IIII IIII

LST

Load status register ST0, direct or indirect 1 2 0000 1110 IAAA AAAA

Load status register ST1, direct or indirect 1 2 0000 1111 IAAA AAAA

NOP No operation 1 1 1000 1011 0000 0000

POP

Pop top of stack to low ACC 1 1 1011 1110 0011 0010