Central Arithmetic Logic Section

3-11

Central Processing Unit

3.3.3 Output Data-Scaling Shifter

The output data-scaling shifter (output shifter) has a 32-bit input connected to

the 32-bit output of the accumulator and a 16-bit output connected to the data

bus. The shifter copies all 32-bits of the accumulator and then performs a left

shift on its content; it can be shifted from zero to seven bits, as specified in the

corresponding store instruction. The upper word (SACH instruction) or lower

word (SACL instruction) of the shifter is then stored to data memory. The con-

tent of the accumulator remains unchanged.

When the output shifter performs the shift, the MSBs are lost and the LSBs are

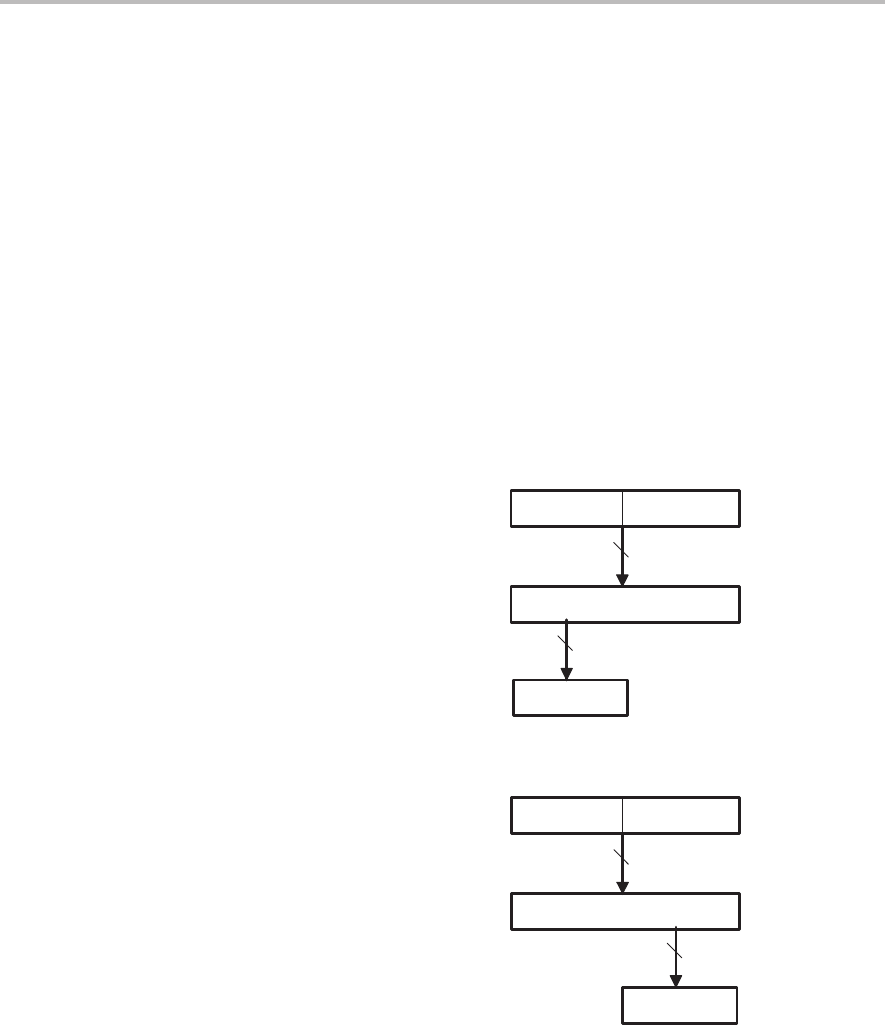

zero filled. Figure 3–7 shows an example in which the accumulator value is

shifted left by four bits and the shifted high word is stored to data memory.

Figure 3–8 shows the same accumulator value shifted left by 6 bits and then

the shifted low word stored.

Figure 3–7. Shifting and Storing the High Word of the Accumulator

Data-memory

location

0 0 F 0

F 0 A 1

0 F 0 F

0 A 1 0

32

Output shifter

(left shift by 4 bits)

Accumulator

16

0 F 0 F

Figure 3–8. Shifting and Storing the Low Word of the Accumulator

Data-memory

location

0 0 F 0

F 0 A 1

3 C 3 C

2 8 4 0

32

Output shifter

(left shift by 6 bits)

Accumulator

16

2 8 4 0