Input Scaling Section

3-3

Central Processing Unit

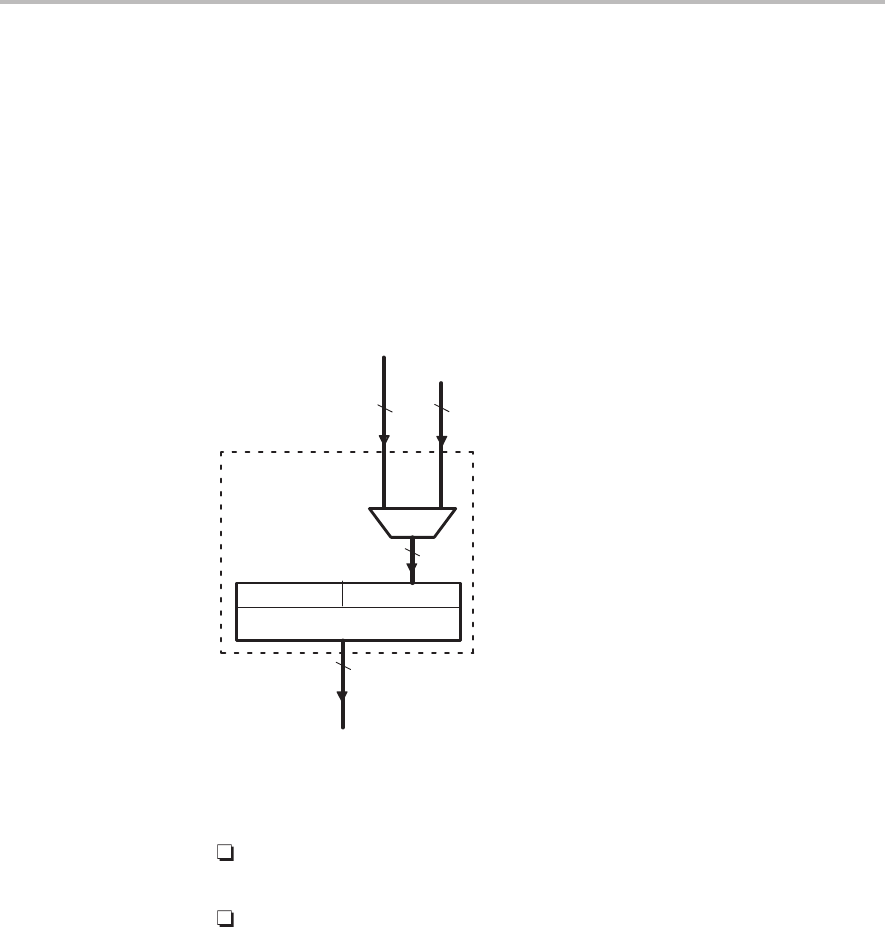

3.1 Input Scaling Section

A 32-bit input data-scaling shifter (input shifter) aligns a 16-bit value coming

from memory to the 32-bit CALU. This data alignment is necessary for data-

scaling arithmetic as well as aligning masks for logical operations. The input

shifter operates as part of the data path between program or data space and

the CALU and, thus, requires no cycle overhead. Described directly below are

the input, the output, and the shift count of the input shifter. Throughout the dis-

cussion, refer to Figure 3–2.

Figure 3–2. Block Diagram of the Input Scaling Section

Input shifter (32 bits)

16

32

16

MUX

31

016 15

Input scaling

section

16

From data memory (DRDB)

From program memory (PRDB)

To CALU

Input. Bits 15 through 0 of the input shifter accept a 16-bit input from either of

two sources (see Figure 3–2):

The data read bus (DRDB).

This input is a value from a data memory loca-

tion referenced in an instruction operand.

The program read bus (PRDB).

This input is a constant value given as an

instruction operand.

Output. After a value has been accepted into bits 15 through 0, the input shifter

aligns the16-bit value to the 32-bit bus of the CALU as shown in Figure 3–2.

The shifter shifts the value left 0 to 16 bits and then sends the 32-bit result to

the CALU.

During the left shift, unused LSBs in the shifter are filled with zeros, and unused

MSBs in the shifter are either filled with zeros or sign extended, depending on

the value of the sign-extension mode bit (SXM) of status register ST1.