’C209 On-Chip Peripherals

11-17

TMS320C209

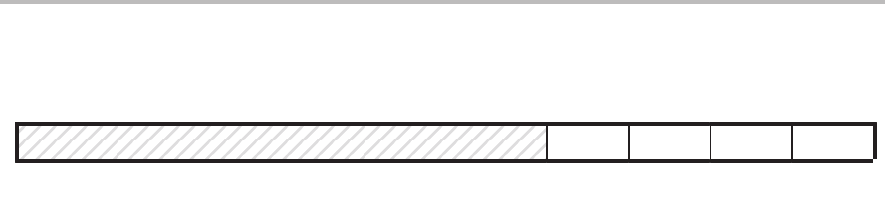

Figure 11–5.’C209 Wait-State Generator Control Register (WSGR) — I/O Address FFFFh

15–4 3 2 1 0

Reserved AVIS ISWS DSWS PSWS

0 W–1 W–1 W–1 W–1

Note: 0 = Always read as zeros; W = Write access; value following dash (–) is value after reset.

Bits 15–4 Reserved. Bits 15–4 are reserved and are always read as 0s.

Bit 3 AVIS — Address visibility mode. AVIS = 1 enables the address visibility mode of

the device. In this mode, the device provides a method of tracing internal code opera-

tion: it passes the internal program address to the address bus when this bus is not

used for an external access. At reset, AVIS is set to 1. For production systems, the

AVIS bit should be cleared to 0 to reduce power and noise. (AVIS does not generate

a wait state.)

Bit 2 ISWS — I/O-space wait-state bit. When ISWS = 1, one wait state will be applied to

all reads from off-chip I/O space. When ISWS = 0, no wait states are generated for

off-chip I/O space. At reset, this bit is set to 1.

Bit 1 DSWS — Data-space wait-state bit. When DSWS = 1, one wait state will be applied

to all reads from off-chip data space. When DSWS = 0, no wait states are generated

for off-chip data space. At reset, this bit is set to 1.

Bit 0 PSWS — Program-space wait-state bit. When PSWS = 1, one wait state will be ap-

plied to all reads from off-chip program space. When PSWS = 0, no wait states are

generated for off-chip program space. At reset, this bit is set to 1.