Components and Basic Operation

9-5

Synchronous Serial Port

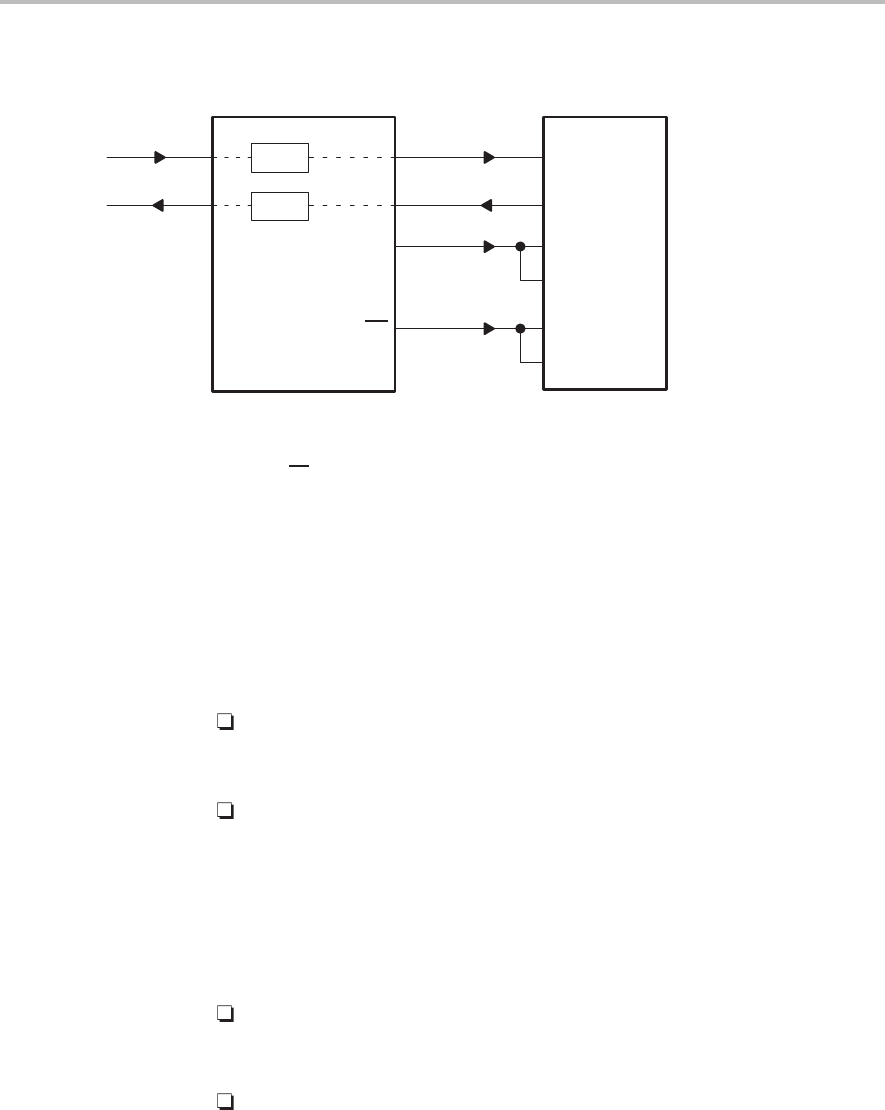

Figure 9–2. 2-Way Serial Port Transfer With External Frame Sync and External Clock

TMS320C203

TLC320AD55C

Analog

signal

A/D

D/A

Analog

signal

DR

DX

CLKX

CLKR

FSX

FSR

D

OUT

D

IN

SCK

FS

Legend: D

OUT

Transmit data DR Receive data

D

IN

Receive data DX Transmit data

SCK Clock source CLKX Transmit clock

FS

Frame sync source CLKR Receive clock

FSX Transmit frame synchronization

FSR Receive frame synchronization

9.2.2 FIFO Buffers and Registers

The synchronous serial port (SSP) has two four-level transmit and receive

FIFO buffers (shown at the center of Figure 9–1 on page 9-3).

Two on-chip registers allow you to access the FIFO buffers and control the op-

eration of the port:

Synchronous data transmit and receive register (SDTR). The SDTR,

at I/O address FFF0h, is used for the top of both FIFO buffers (transmit and

receive) and is the only visible part of the FIFO buffers.

Synchronous serial port control register (SSPCR). The SSPCR, at I/O

address FFF1h, contains bits for setting port modes, indicating the status

of a data transfer, setting trigger conditions for interrupts, indicating error

conditions, accepting bit input, and resetting the port. Section 9.3 includes

a detailed description of the SSPCR.

Two other registers (not accessible to a programmer) control transfers be-

tween the FIFO buffers and the pins:

Synchronous serial port transmit shift register (XSR). Each data word

is transferred from the bottom level of the transmit FIFO buffer to the XSR.

The XSR then shifts the data out (MSB first) through the DX pin.

Synchronous serial port receive shift register (RSR). Each data word

is accepted, one bit at a time, at the DR pin and shifted into the RSR. The

RSR then transfers the word to the bottom level of the receive FIFO buffer.