LAR

Load Auxiliary Register

7-80

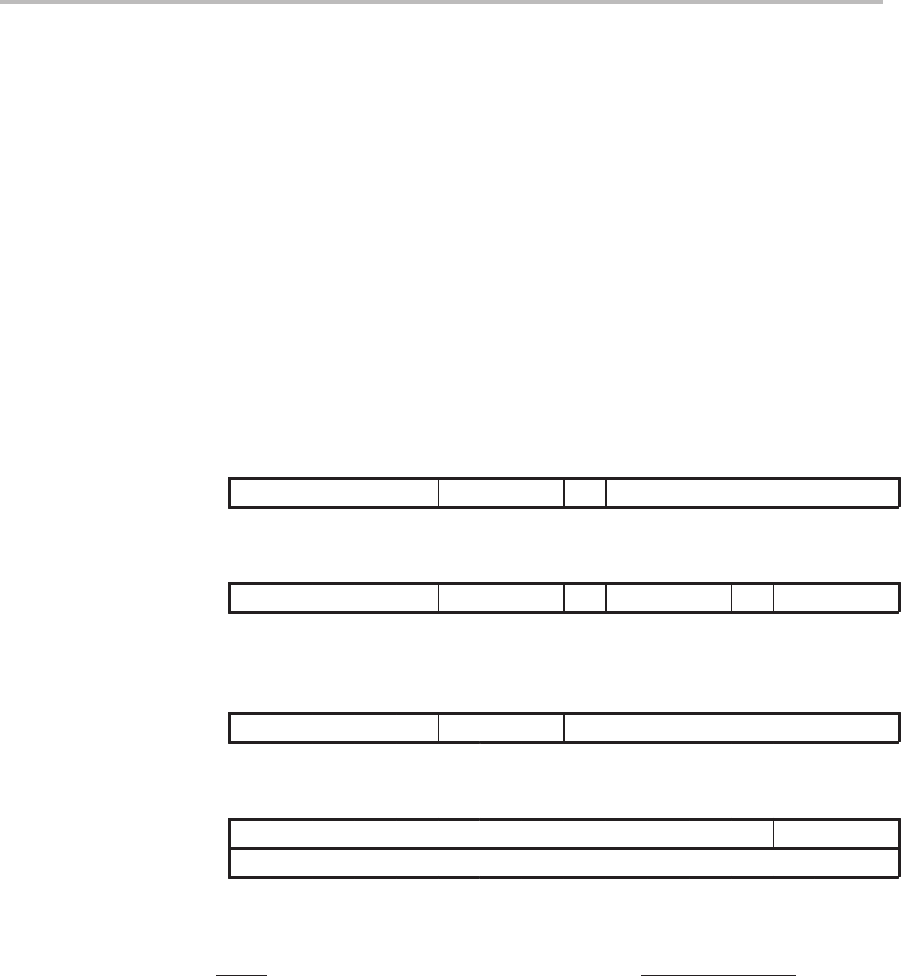

Syntax LAR AR

x

,

dma

Direct addressing

LAR AR

x

,

ind

[, AR

n

] Indirect addressing

LAR AR

x

, #

k

Short immediate addressing

LAR AR

x

, #

lk

Long immediate addressing

Operands x: Value from 0 to 7 designating the auxiliary register to be loaded

dma: 7 LSBs of the data-memory address

k: 8-bit short immediate value

lk: 16-bit long immediate value

n: Value from 0 to 7 designating the next auxiliary register

ind: Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

LAR AR

x

,

dma

1514131211109876543210

0

0000 x 0 dma

LAR AR

x

,

ind

[, AR

n

]

1514131211109876543210

0

0000 x 1 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

LAR AR

x

,

#

k

1514131211109876543210

1

0110 x k

LAR AR

x

,

#

lk

1514131211109876543210

1

011111100001 x

lk

Execution Increment PC, then ...

Event Addressing mode

(data-memory address) → ARx Direct or indirect

k → ARx Short immediate

lk → ARx Long immediate

Status Bits None

Opcode