Return Conditionally

RETC

7-143

Assembly Language Instructions

Syntax RETC

cond

1 [,

cond

2] [

,...

]

Operands

cond Condition

EQ ACC = 0

NEQ ACC ≠ 0

LT ACC < 0

LEQ ACC ≤ 0

GT ACC > 0

GEQ ACC ≥ 0

NC C = 0

CC =1

NOV OV = 0

OV OV = 1

BIO BIO

low

NTC TC = 0

TC TC = 1

UNC Unconditionally

‡

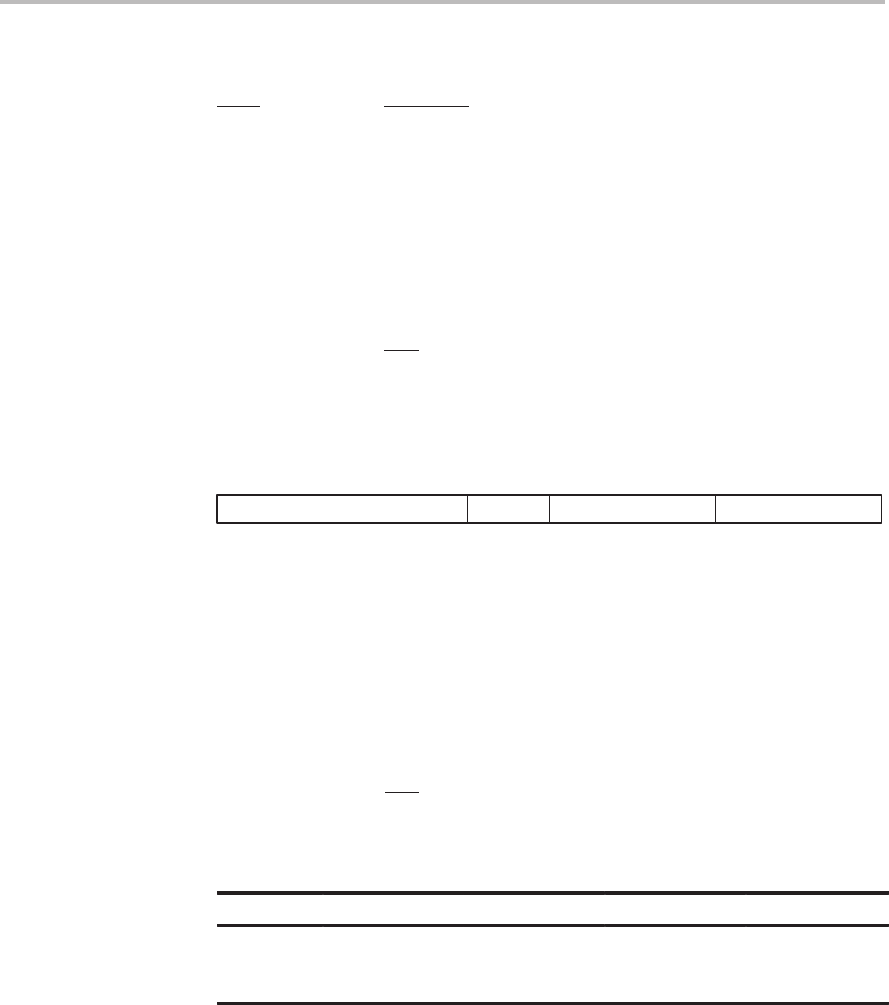

Opcode

0123456789101112131415

ZLVCZLVCTP110111

Note: The TP and ZLVC fields are defined on pages 7-3 and 7-4.

Execution If

cond

1 AND

cond

2 AND ...

(TOS) → PC

Pop stack one level

Else, continue

Status Bits None

Description If the specified condition or conditions are met, a standard return is executed

(see the description for the RET instruction). Note that not all combinations of

conditions are meaningful. For example, testing for LT and GT is contradictory.

In addition, testing BIO

is mutually exclusive to testing TC.

Words 1

Cycles for a Single RETC Instruction

Condition ROM DARAM SARAM External

True 4 4 4 4+4p

False 2 2 2 2+2p

Note: The processor performs speculative fetching by reading two additional instruction

words. If the PC discontinuity is taken, these two instruction words are discarded.

Example RETC GEQ,NOV ;A return is executed if the

;accumulator content is positive

;or zero and if the OV (overflow)

;-bit is zero.

Cycles