RPT

Repeat Next Instruction

7-146

Syntax RPT

dma

Direct addressing

RPT

ind

[, AR

n

] Indirect addressing

RPT #

k

Short immediate

Operands dma: 7 LSBs of the data-memory address

n: Value from 0 to 7 designating the next auxiliary register

k: 8-bit short immediate value

ind: Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

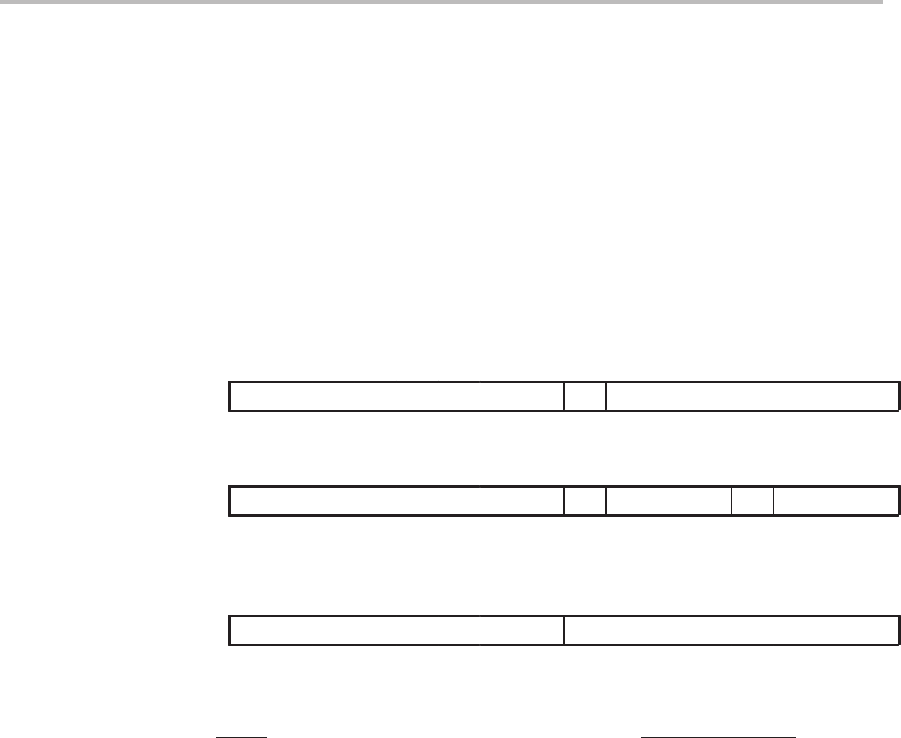

RPT

dma

1514131211109876543210

0

00010110 dma

RPT

ind

[, AR

n

]

1514131211109876543210

0

00010111 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

RPT #

k

1514131211109876543210

1

0111011 k

Execution Increment PC, then ...

Event Addressing mode

(data-memory address) → RPTC Direct or indirect

k → RPTC Short immediate

Status Bits None

Description The repeat counter (RPTC) is loaded with the content of the addressed data-

memory location if direct or indirect addressing is used; it is loaded with an 8-bit

immediate value if short immediate addressing is used. The instruction follow-

ing the RPT is repeated

n

times, where

n

is the initial value of the RPTC plus

1. Since the RPTC cannot be saved during a context switch, repeat loops are

regarded as multicycle instructions and are not interruptible. The RPTC is

cleared to 0 on a device reset.

RPT is especially useful for block moves, multiply/accumulates, and normal-

ization. The repeat instruction itself is not repeatable.

Words 1

Opcode