Receiver Operation

10-20

10.5 Receiver Operation

The receiver includes two internal 8-bit registers: the receive register (ADTR)

and receive shift register (ARSR). The data received at the RX pin should have

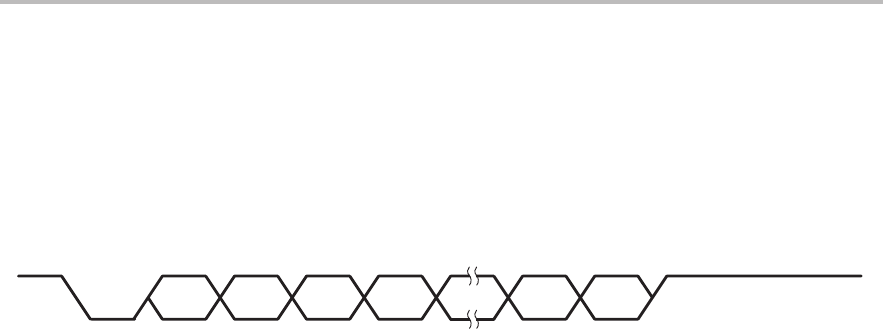

the serial form shown in Figure 10–7 (the number of stop bits required de-

pends on the value of the STB bit in the ASPCR).

Figure 10–7. Data Receive

Start Bit 0 Bit 1 Bit 2 Bit 3 Bit 6 Bit 7 Stop 1 Stop 2

Data is received on the RX pin, and the negative-edge detect logic initiates a

receive operation and checks for a start bit. After the eight data bits are re-

ceived, a stop bit (or bits) should be received, indicating the end of that block.

If a valid stop bit is not received, a framing error has occurred; in response, the

FE bit in the ASPCR is set to 1, and a TXRXINT interrupt is generated. Then

normal reception continues, and the receiver looks for the next start bit.

Once a valid stop bit is received, data is then transferred to the ADTR, and an

interrupt (TXRXINT) is sent to the CPU. The DR bit of the IOSR is set to indi-

cate that a character has been received in the receive register, ADTR. (DR is

cleared to 0 when the ADTR is read.) The ARSR is now available to receive

another character.

If ADTR is not read before new data is transferred into the ADTR, the overflow

error (OE) flag is set in the IOSR.

In summary, asynchronous mode reception involves the following events:

1) A negative edge is received on RX to indicate a start bit. A test is performed

to indicate whether a start bit is valid.

2) If the start bit is valid, eight data bits are shifted into ARSR (LSB first).

3) A stop bit is received to indicate end of reception. (If a stop bit is not re-

ceived, a framing error is indicated.)

4) Data is transferred from ARSR to ADTR.

5) An interrupt is sent to the CPU once data has been placed in the ADTR.

6) Reception is complete. The receiver waits for another negative transition.

To avoid double interrupts, the interrupt service routine should clear TXRXINT

in the interrupt flag register (IFR) just before forcing a return from the routine.