Load Status Register

LST

7-89

Assembly Language Instructions

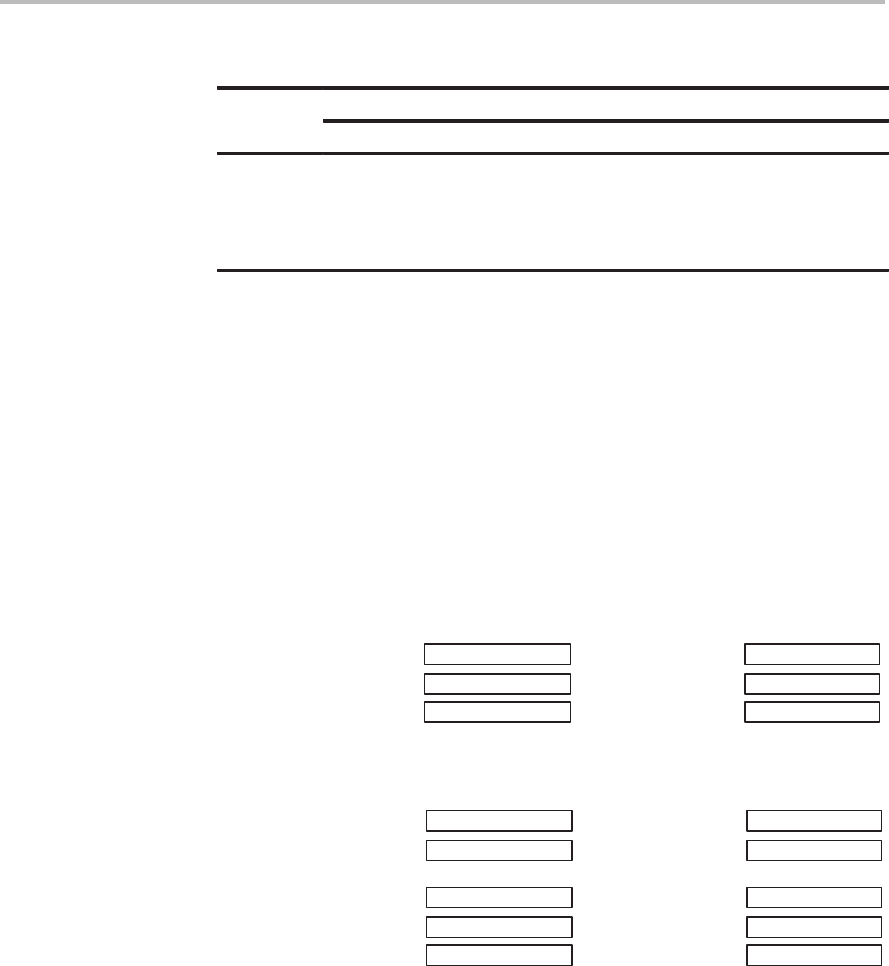

Cycles for a Repeat (RPT) Execution of an LST Instruction

Program

Operand ROM DARAM SARAM External

DARAM 2n 2n 2n 2n+p

code

SARAM 2n 2n 2n, 2n+1

†

2n+p

code

External 2n+nd

src

2n+nd

src

2n+nd

src

2n+1+nd

src

+p

code

†

If the operand and the code are in the same SARAM block

Example 1 MAR *,AR0

LST #0,*,AR1 ;The data memory word addressed by the

;contents of auxiliary register AR0 is

;loaded into status register ST0,except

;for the INTM bit. Note that even

;though a next ARP value is specified,

;that value is ignored. Also note that

;the old ARP is not loaded into the

;ARB.

Example 2 LST #0,60h ;(DP = 0)

Before Instruction After Instruction

Data Memory Data Memory

60h 2404h 60h 2404h

ST0 6E00h ST0 2604h

ST1 05ECh ST1 05ECh

Example 3 LST #0,*–,AR1

Before Instruction After Instruction

ARP 4 ARP 7

AR4 3FFh AR4 3FEh

Data Memory Data Memory

3FFh EE04h 3FFh EE04h

ST0 EE00h ST0 EE04h

ST1 F7ECh ST1 F7ECh