SST

Store Status Register

7-172

Syntax SST #

m

,

dma

Direct addressing

SST #

m

,

ind

[,

AR

n

] Indirect addressing

Operands dma: 7 LSBs of the data-memory address

n: Value from 0 to 7 designating the next auxiliary register

m: Select one of the following:

0 Indicates that ST0 will be stored

1 Indicates that ST1 will be stored

ind: Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

SST #0,

dma

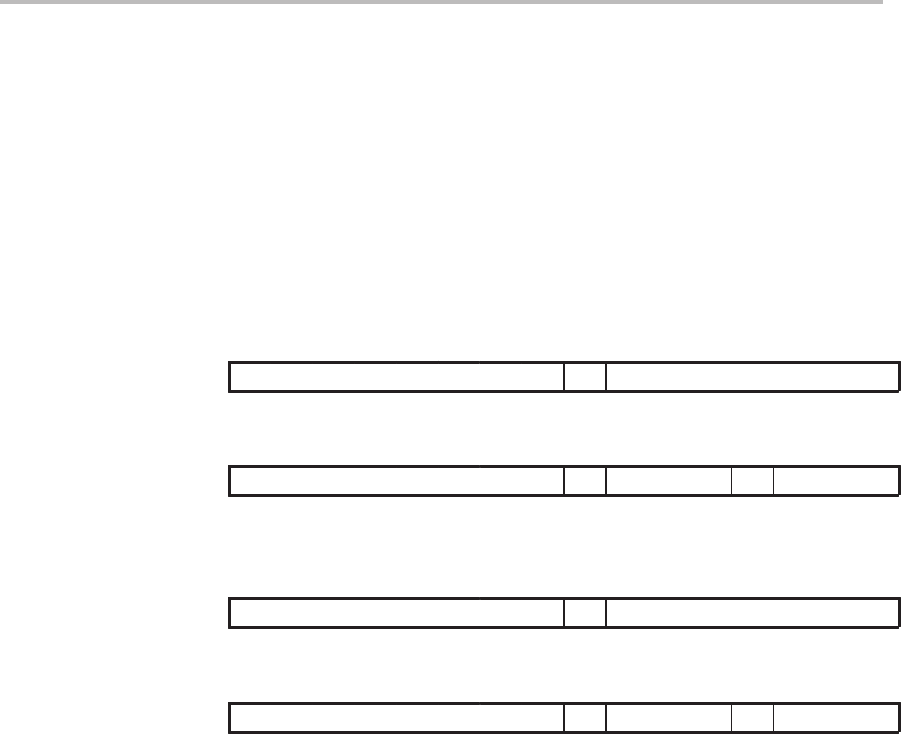

1514131211109876543210

1

00011100 dma

SST #0

, ind

[, AR

n

]

1514131211109876543210

1

00011101 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

SST #1,

dma

1514131211109876543210

1

00011110 dma

SST #1

, ind

[, AR

n

]

1514131211109876543210

1

00011111 ARU N NAR

Note: ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode

(page 6-9).

Execution Increment PC, then ...

(status register STm) → data-memory address

Status Bits None

Description Status register ST0 or ST1 (whichever is specified) is stored in data memory.

In direct addressing mode, the specified status register is always stored in

page 0, regardless of the value of the data page pointer (DP) in ST0. Although

the processor automatically accesses page 0, the DP is not physically modi-

fied; this allows the DP value to be stored unchanged when ST0 is stored. The

specific storage location within page 0 is given in the instruction.

In indirect addressing mode, the storage address is obtained from the auxiliary

register selected; thus, the specified status register contents can be stored to

an address on any page in data memory.

Opcode