Set PREG Output Shift Mode

SPM

7-167

Assembly Language Instructions

Syntax SPM

constant

Operands constant: Value from 0 to 3 that determines the product shift mode

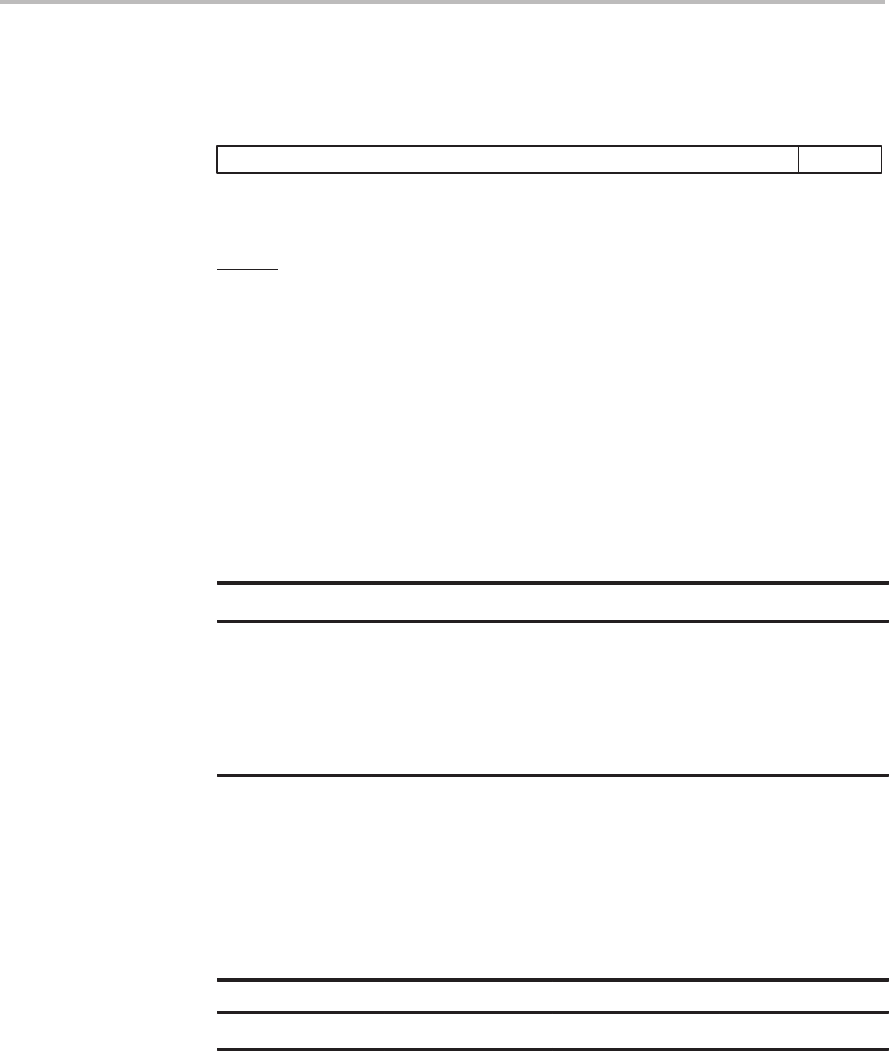

Opcode

constant00000011111101

0123456789101112131415

Execution Increment PC, then ...

constant → product shift mode (PM) bits

Status Bits

Affects

PM

This instruction is not affected by SXM.

Description The two LSBs of the instruction word are copied into the product shift mode

(PM) bits of status register ST1 (bits 1 and 0 of ST1). The PM bits control the

mode of the shifter at the output of the PREG. This shifter can shift the PREG

output either one or four bits to the left or six bits to the right. The possible PM

bit combinations and their meanings are shown in Table 7–8. When an instruc-

tion accesses the PREG value, the value first passes through the shifter,

where it is shifted by the specified amount.

Table 7–8. Product Shift Modes

PM Field Specified Product Shift

00 No shift of PREG output

01 PREG output to be left shifted 1 place

10 PREG output to be left shifted 4 places

11

PREG output to be right shifted 6 places and sign extended

The left shifts allow the product to be justified for fractional arithmetic. The

right-shift-by-six mode allows up to 128 multiply accumulate processes with-

out the possibility of overflow occurring. PM may also be loaded by an LST #1

instruction.

Words 1

Cycles for a Single SPM Instruction

ROM

DARAM SARAM External

1 1 1 1+p

Example SPM 3 ;Product register shift mode 3 (PM = 11)

;is selected causing all subsequent

;transfers from the product register (PREG)

;to be shifted to the right six places.

Cycles