Timer

8-11

On-Chip Peripherals

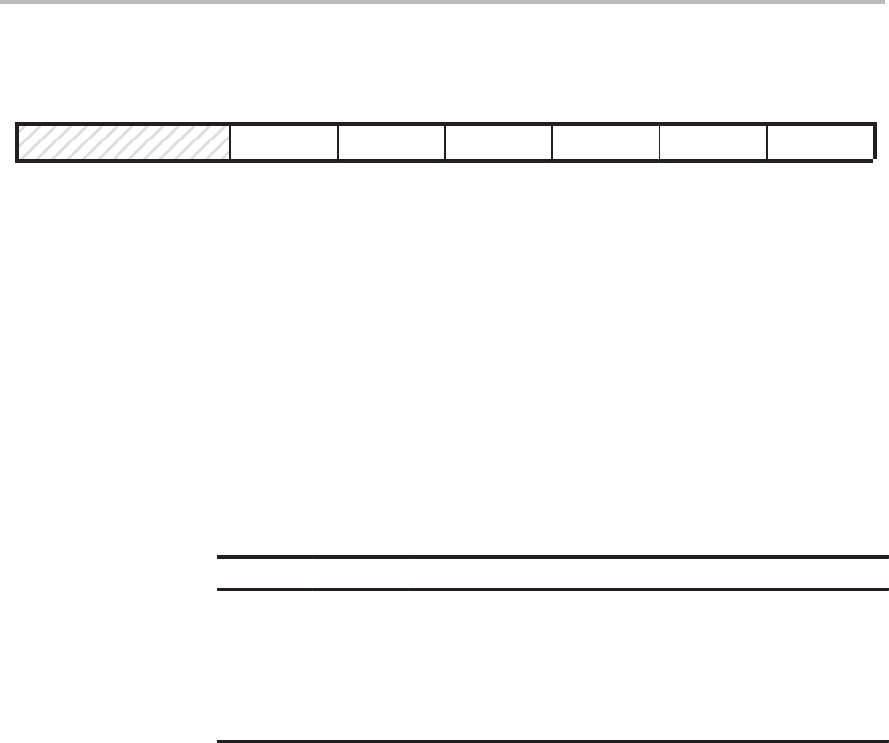

Figure 8–5. ’C2xx Timer Control Register (TCR) — I/O-Space Address FFF8h

15 12 11 10 965 430

Reserved FREE SOFT PSC TRB TSS TDDR

0 R/W–0 R/W–0 R/W–0 R/W–0 W–0 R/W–0

Note: 0 = Always read as zeros; R = Read access; W = Write access; value following dash (–) is value after reset.

Bits 15–12 Reserved. Bits 15–12 are reserved and are always read as 0s.

Bits 11–10 FREE, SOFT — These bits are special emulation bits that determine the

state of the timer when a breakpoint is encountered in the high-level lan-

guage debugger. If the FREE bit is set to 1, then, upon a software breakpoint,

the timer continues to run (that is, free runs). In this case, SOFT is a

don’t

care

. But if FREE is 0, then SOFT takes effect. In this case, if SOFT = 0, the

timer halts the next time the TIM decrements. If the SOFT bit is 1, then the

timer halts when the TIM has decremented to zero. Table 8–3 summarizes

the available run and emulation modes. The default (reset) setting is

FREE = 0 and SOFT = 0.

Table 8–3. ’C2xx Timer Run/Emulation Modes

FREE SOFT Timer Run/Emulation Mode

0 0 Stop after the next decrement of the TIM (hard stop)

0 1 Stop after the TIM decrements to 0 (soft stop)

1 0 Free run

1 1 Free run

Bits 9–6 PSC — Timer prescaler counter. These four bits hold the current prescale

count for the timer. For every CLKOUT1 cycle that the PSC value is greater

than 0, the PSC decrements by one. One CLKOUT1 cycle after the PSC

reaches 0, the PSC is loaded with the contents of the TDDR, and the timer

counter register (TIM) decrements by one. The PSC is also reloaded when-

ever the timer reload bit (TRB) is set by software. The PSC can be checked

by reading the TCR, but it cannot be set directly. It must get its value from

the timer divide-down register (TDDR). At reset, the PSC is set to 0.

Bit 5 TRB — Timer reload bit. When you write a 1 to TRB, the TIM is loaded with

the value in the PRD, and the PSC is loaded with the value in the timer divide-

down register (TDDR). The TRB bit is always read as zero.