Register Descriptions

A-13

Register Summary

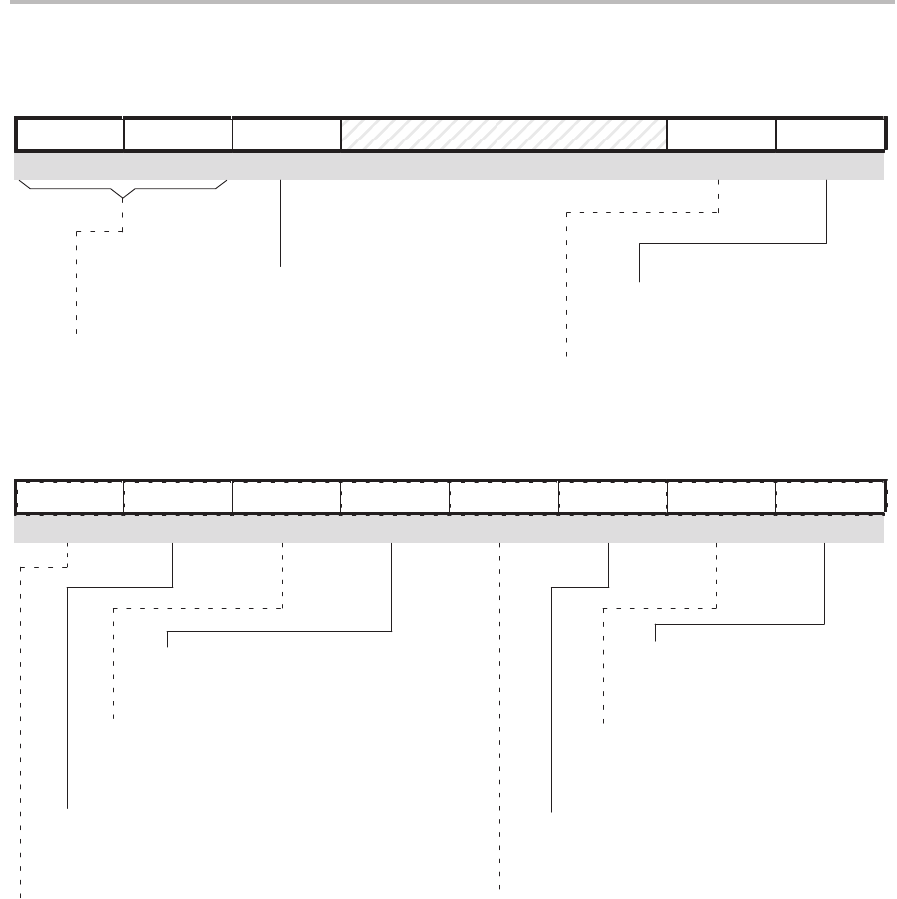

Asynchronous Serial Port Control Register (ASPCR) — I/O Address FFF5h

15 14 13 12 11 10 9 8

0 0 0 0 0 0

FREE SOFT URST Reserved

†

DIM TIM

Immediate stop

Process stops after character completion.

Free run

Free run

0

1

Port in reset

Port enabled

Disables transmit interrupts

Enables transmit interrupts

0

1

Disables delta interrupts

Enables delta interrupts

0

1

0

1

0

1

0

0

1

1

Emulation/run mode

R/WR/W

R/W R/W R/W

Port reset

Delta interrupt mask

Transmit interrupt mask

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0

RIM STB CAD SETBRK CIO3 CIO2 CIO1 CIO0

0

1

Disables receive interrupts

Enables receive interrupts

0

1

One stop bit for transmission and reception

Two stop bits for transmission and reception

0

1

Disables auto-baud alignment

Enables auto-baud alignment when ADC = 0

0

1

TX output forced high

TX output forced low

0

1

IO3 configured as input

IO3 configured as output

0

1

IO2 configured as input

IO2 configured as output

0

1

IO1 configured as input

IO1 configured as output

0

1

IO0 configured as input

IO0 configured as output

R/W R/W R/W R/W R/W R/W R/W R/W

Receive interrupt mask

Number of stop bits

Auto-baud alignment

TX pin level between transmissions

IO3 pin configuration

IO2 pin configuration

IO1 pin configuration

IO0 pin configuration

†

These reserved bits are always read as 0s. Writes have no effect.