Programmer’s Reference

ARM DUI 0224F Copyright © 2003-2007 ARM Limited. All rights reserved. 4-25

4.3.6 100Hz Counter, SYS_100HZ

The SYS_100HZ register at

0x10000024

is a 32-bit counter incremented at 100Hz. The

100Hz reference is derived from the 32KHz crystal oscillator. The register is set to zero

by a reset.

4.3.7 Configuration registers SYS_CFGDATAx

The read/write registers SYS_CFGDATA1 and SYS_CFGDATA2 contain

configuration data that is applied to the ARM926EJ-S PXP Development Chip

HDATAM1 and HDATAM2 pins when the DEV CHIP RECONFIG pushbutton is

pressed.

In a production ASIC, the configuration signals would be tied HIGH or LOW, but they

are configurable in the ARM926EJ-S PXP Development Chip. This enables you to test

different build options. For example, you can simulate a system that boots in big-endian

or with the vector table located at address

0xFFFF0000

by changing the value of bits 0 and

1 in the SYS_CFGDATA2 register and pressing the SDC RECONFIG button.

For details on the configuration process, see Configuration from the DEV CHIP

RECONFIG pushbutton on page 3-9.

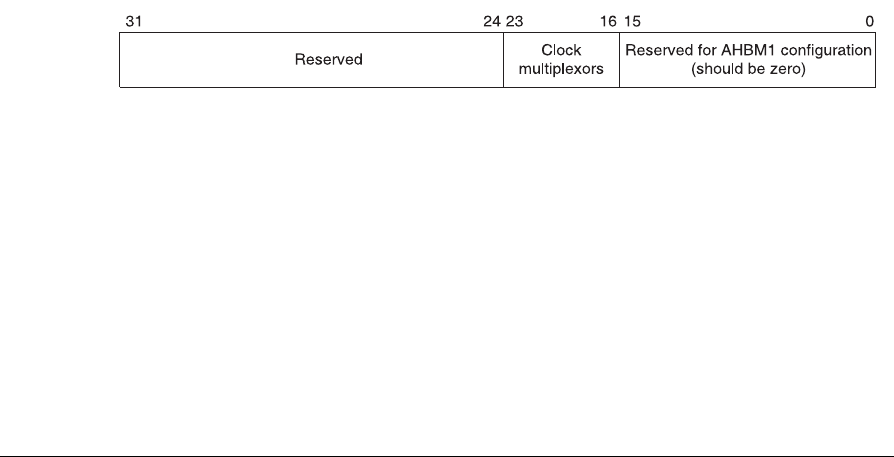

SYS_CFGDATA1 at address

0x10000028

contains the configuration settings to apply to

HDATA1 pins and the clock multiplexing logic. Figure 4-11 and Table 4-8 on page 4-26

show the configuration signals for each bit and the default value loaded at power on

reset.

Figure 4-11 SYS_CFGDATA1