Programmer’s Reference

4-58 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

4.11.1 Primary interrupt controller

The primary interrupt control registers are listed in Table 4-39. For more detail on the

primary interrupt controller, see the ARMPL190 VIC Technical Reference Manual.

DMA NA

Release version custom logic

Reference documentation Secondary interrupt controller on page 4-61 and Interrupts on

page 3-72)

Table 4-38 SIC implementation (continued)

Property Value

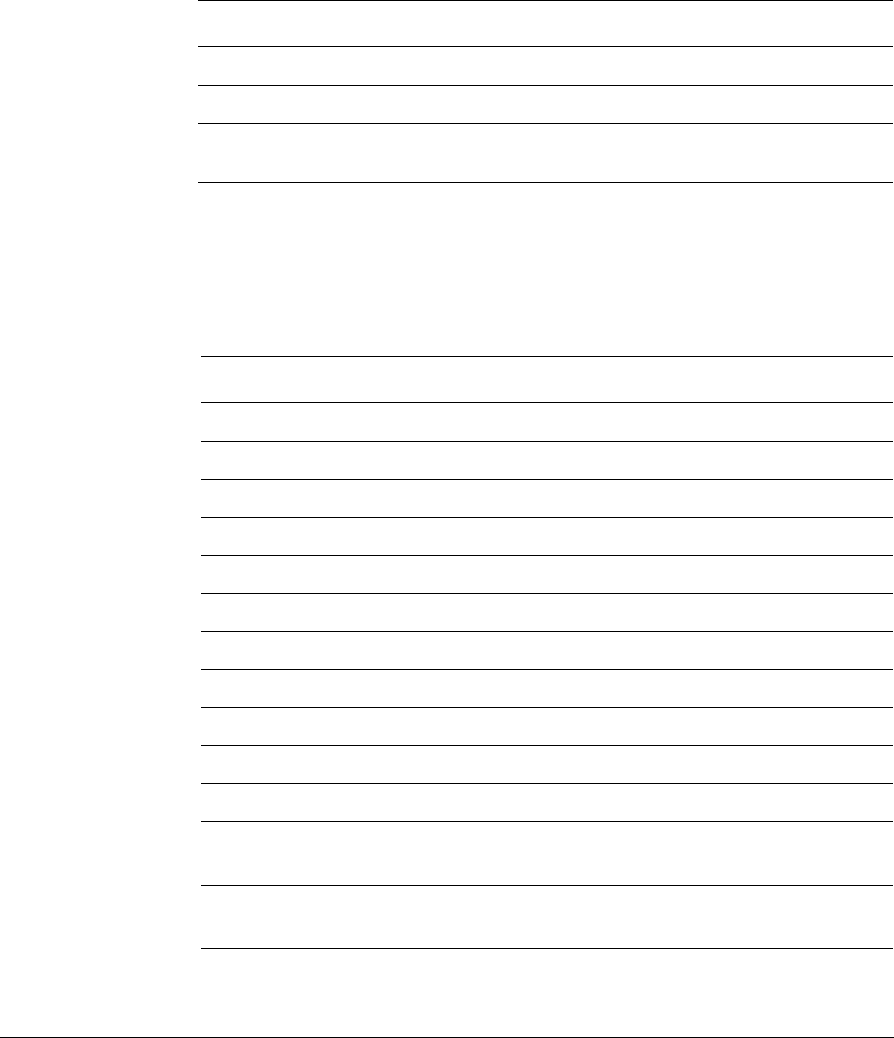

Table 4-39 Primary interrupt controller registers

Address Name Access Description

0x10140000

PICIRQStatus Read IRQ status register

0x10140004

PICFIQStatus Read FIQ status register

0x10140008

PICRawIntr Read Raw interrupt status register

0x1014000C

PICIntSelect Read/write Interrupt select register

0x10140010

PICIntEnable Read/write Interrupt enable register

0x10140014

PICIntEnClear Write Interrupt enable clear register

0x10140018

PICSoftInt Read/write Software interrupt register

0x1014001C

PICSoftIntClear Write Software interrupt clear register

0x10140020

PICProtection Read/write Protection enable register

0x10140030

PICVectAddr Read/write Vector address register

0x10140034

PICDefVectAddr Read/write Default vector address register

0x10140100

–

0x1014013C

PICVectAddr0–

PICVectAddr15

Read/write Vector address 0 register to

Vector address 15 register

0x10140200

–

0x1014023C

PICVectCntl0–

PICVectCntl15

Read/write Vector control 0 register to

Vector control 15 register