Programmer’s Reference

ARM DUI 0224F Copyright © 2003-2007 ARM Limited. All rights reserved. 4-59

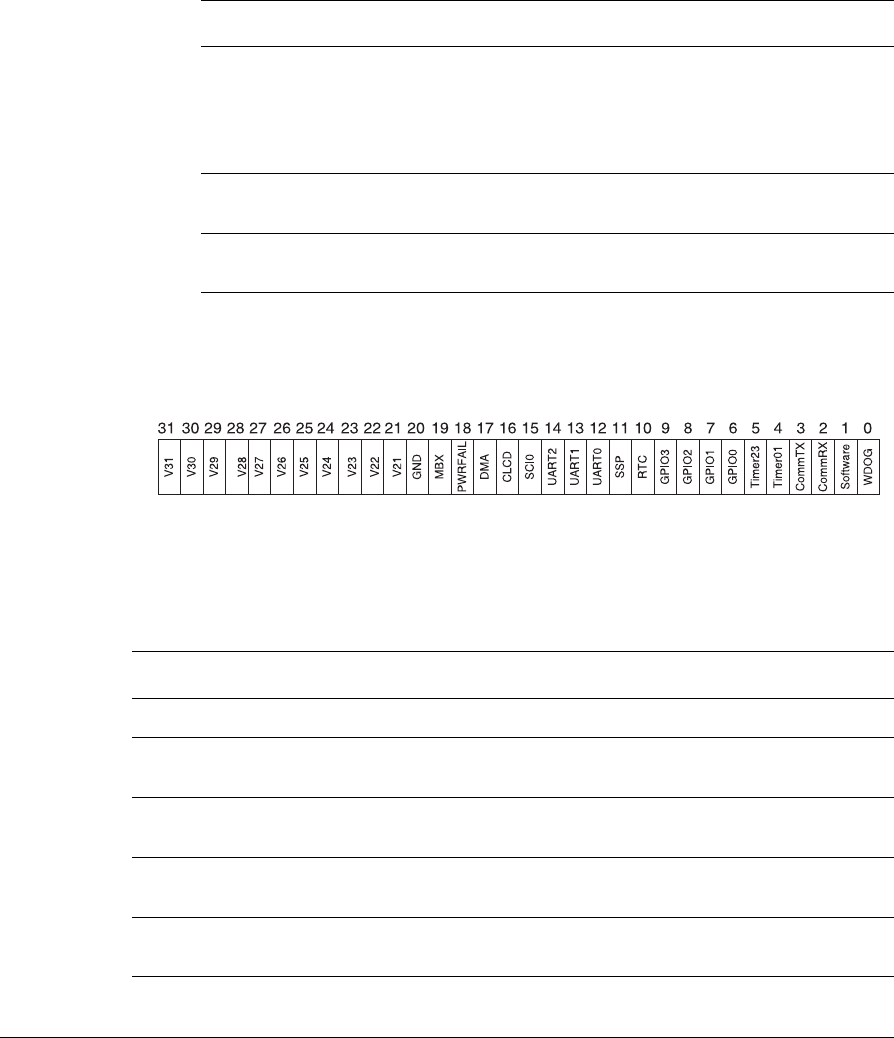

The bit assignments for the primary interrupt controller are shown in Figure 4-23 and

Table 4-40. Each bit corresponds to an interrupt source. Use the bit to enable or disable

the interrupt or to check the interrupt status.

Figure 4-23 Primary interrupt registers

0x10140300

–

0x10140310

PICITCR,

PICITIP1,

PICITIP2,

PICITOP1,

PICITOP2,

Read/write Test control registers

0x10140FE0–

0x10140FEC

PICPeriphID0–

PICPeriphID3

Read Peripheral identification registers

0x10140FF0

–

0x10140FFC

PICPCellID0–

PICPCellID3

Read PrimeCell identification registers

Table 4-39 Primary interrupt controller registers (continued)

Address Name Access Description

Table 4-40 Interrupt signals to primary interrupt controller

Bit

Interrupt source

a

Description

[31] VICINTSOURCE31 External interrupt from secondary controller

[30] VICINTSOURCE30 External interrupt signal from RealView Logic Tile or PCI3

interrupt signal

[29] VICINTSOURCE29 External interrupt signal from RealView Logic Tile or PCI2

interrupt signal

[28] VICINTSOURCE28 External interrupt signal from RealView Logic Tile or PCI1

interrupt signal

[27] VICINTSOURCE27 External interrupt signal from RealView Logic Tile or PCI0

interrupt signal