Programmer’s Reference

4-60 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

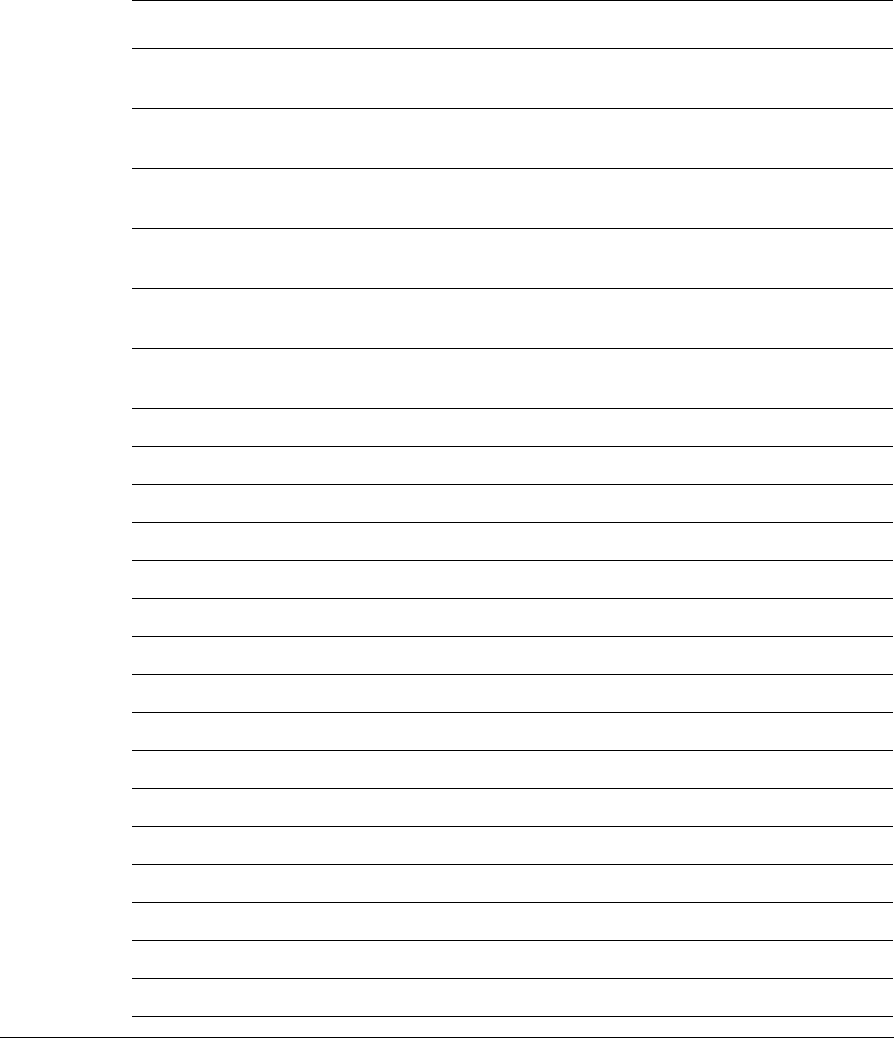

[26] VICINTSOURCE26 External interrupt signal from RealView Logic Tile or USB

interrupt signal

[25] VICINTSOURCE25 External interrupt signal from RealView Logic Tile or

ETHERNET interrupt signal

[24] VICINTSOURCE24 External interrupt signal from RealView Logic Tile or AACI

interrupt signal

[23] VICINTSOURCE23 External interrupt signal from RealView Logic Tile or MCI1A

interrupt signal

[22] VICINTSOURCE22 External interrupt signal from RealView Logic Tile or MCI0A

interrupt signal

[21] VICINTSOURCE21 External interrupt signal from RealView Logic Tile or

DiskOnChip interrupt signal

[20] GND Reserved

[19] MBX Graphics processor on development chip

[18] PWRFAIL Power failure from FPGA

[17] DMA DMA controller in development chip

[16] CLCD CLCD controller in development chip

[15] SCI0 Smart Card interface in development chip

[14] UART2 UART2 on development chip

[13] UART1 UART1 on development chip

[12] UART0 UART0 on development chip

[11] SSP Synchronous serial port in development chip

[10] RTC Real time clock in development chip

[9] GPIO3 GPIO controller in development chip

[8] GPIO2 GPIO controller in development chip

[7] GPIO1 GPIO controller in development chip

[6] GPIO0 GPIO controller in development chip

[5] Timer 2 or 3 Timers on development chip

Table 4-40 Interrupt signals to primary interrupt controller (continued)

Bit

Interrupt source

a

Description