Programmer’s Reference

4-62 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

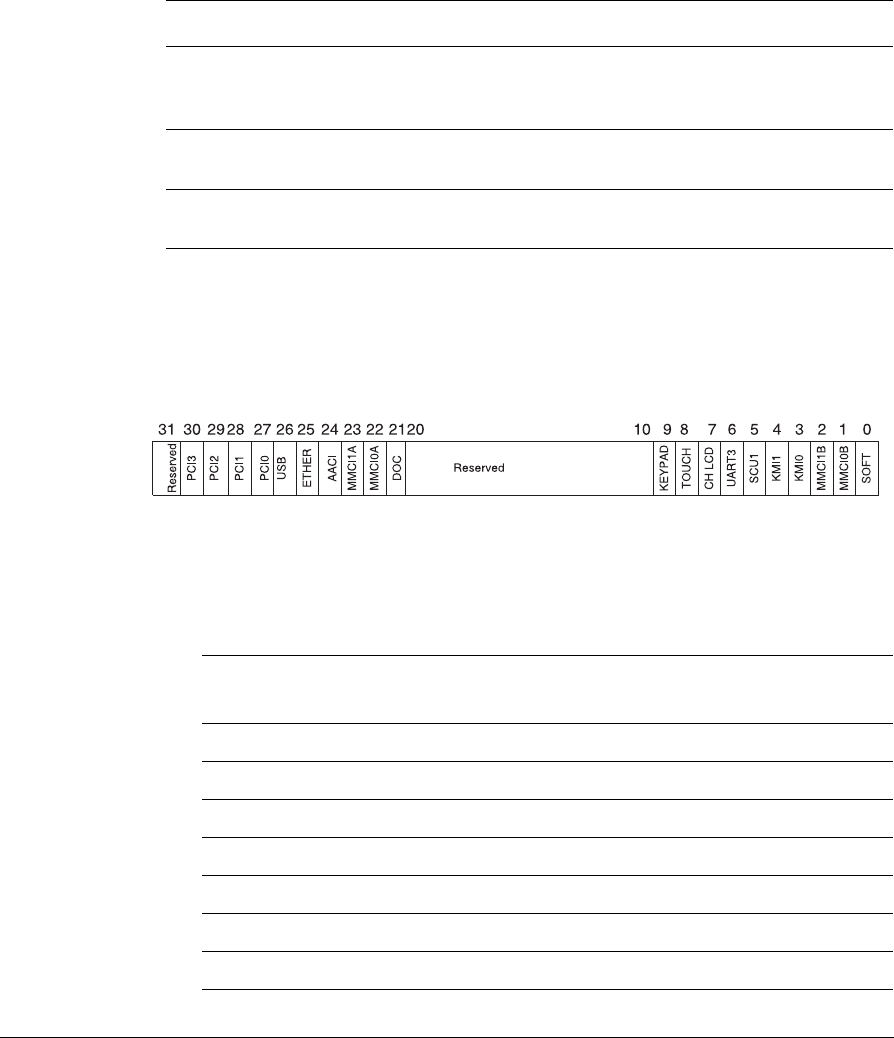

The bit assignments for the secondary interrupt controller are shown in Figure 4-24 and

Table 4-42. Each bit corresponds to an interrupt source. Use the bit to enable or disable

the interrupt or to check the interrupt status. (For the SIC_PICENABLE,

SIC_PICENSET, and SIC_PICENCLR registers, the bits control the pass-through

switches that determine if an interrupt goes only to the SIC or directly to the PCI.)

Figure 4-24 Secondary interrupt registers

0x10003020

SIC_PICENABLE Read Read status of pass-through mask

(allows interrupt to pass directly to the

primary interrupt controller)

0x10003020

SIC_PICENSET Write Set bits HIGH to set the corresponding

interrupt pass-through mask bits

0x10003024

SIC_PICENCLR Write Set bits HIGH to clear the corresponding

interrupt pass-through mask bits

Table 4-41 Secondary interrupt controller registers (continued)

Address Name Access Description

Table 4-42 Interrupt signals to secondary interrupt controller

Bit

Interrupt

source

Description

[31] Reserved NA

[30] PCI3 Interrupt 3 triggered from external PCI bus

[29] PCI2 Interrupt 2 triggered from external PCI bus

[28] PCI1 Interrupt 1 triggered from external PCI bus

[27] PCI0 Interrupt 0 triggered from external PCI bus

[26] USB USB controller ready for data or data available

[25] ETHERNET Ethernet controller ready for data or data available