Hardware Description

3-22 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

3.3 Reset controller

The reset controller initializes the ARM926EJ-S PXP Development Chip, the FPGA,

and external controllers as a result of a reset. The PB926EJ-S can be reset from the

following sources:

• power failure

• reset button

• PCI backplane

•Logic Tiles

•JTAG

• software.

Note

Use the RESET pushbutton (nPBRESET), the JTAG reset signal (nSRST), the PCI

backplane reset signal (P_nRST), the Logic Tile reset signal (nSYSPOR or nSRST

from the tile), or a software reset to reset the ARM926EJ-S core. The current

ARM926EJ-S PXP Development Chip configuration settings are retained. (The effect

of these reset sources pushbutton can be modified by setting the reset level flags, see

Reset level on page 3-24.)

Use the DEV CHIP RECONFIG pushbutton to reset the processor and reload the chip

configuration settings from the FPGA configuration registers.

Use the FPGA CONFIG pushbutton to reload the FPGA image without repowering the

entire system. The FPGA configuration registers are reloaded with their default values.

(Pressing FPGA CONFIG also resets the core and reloads the Logic Tile images.)

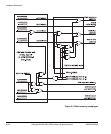

3.3.1 Reset and reconfiguration logic

Figure 3-11 on page 3-23 shows the reset and reconfigure logic. (Not all JTAG reset

signals are shown.)