Hardware Description

ARM DUI 0224F Copyright © 2003-2007 ARM Limited. All rights reserved. 3-27

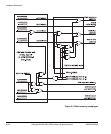

3.3.3 Memory aliasing at reset

Under normal operation, the PB926EJ-S has dynamic memory located at

0x0

. In order

to load the boot code however, non-volatile memory must be remapped to the boot

address.

Remapping the memory is done by changing how the chip select signals in the

ARM926EJ-S PXP Development Chip connect to the external chip select signals that

control memory devices. Figure 3-14 on page 3-28 shows the two stage remapping

process:

•If DEVCHIP REMAP signal is HIGH, from the system controller, it disables the

nMPMCDYCS0 signal that is normally generated by accesses to memory region

0x00000000

–

0x03FFFFFF

.

Accesses to memory region

0x00000000

–

0x03FFFFFF

are remapped to:

— the AHB expansion memory chip select if BOOTCSSEL[1:0] is

b11

— nSTATICCS1 if one of BOOTCSSEL[1:0] is not

b11

.

This remapping occurs inside the ARM926EJ-S PXP Development Chip.

•If FPGA_REMAP is HIGH, from the SYS_MISC register, nSTATICCS1 is

remapped to:

— nDOCCS if BOOTCSSEL[1:0] is

b00

— nNORCS if BOOTCSSEL[1:0] is

b01.

This remapping occurs inside the FPGA.

At reset, the DEVCHIP REMAP and FPGA_REMAP signals are both HIGH.

Which of nDOCCS, nNORCS, or AHB expansion memory is active at reset therefore

depends on the value of the BOOTCSSEL[1:0]. See Remapping of boot memory on

page 4-9.

Note

If the size of the physical memory selected by nDOCCS, nNORCS, or AHB expansion

memory is less than the address range of

0x00000000

–

0x03FFFFFF

, the physical memory

is aliased and repeated to fill the address space.

The static expansion memory selected by nEXPCS2 cannot be used as boot memory.

The expansion memory can be moved to address

0x0

, but the memory no longer appears

at its original location and the code in the boot monitor that jumps to high memory is

not usable.