Specifications

B-6 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

B.2.1 AHB bus timing

Table B-5 lists the timing for the AHB buses. (The bus clock frequency is typically

35MHz for a

t

cyc

of 28.5ns).

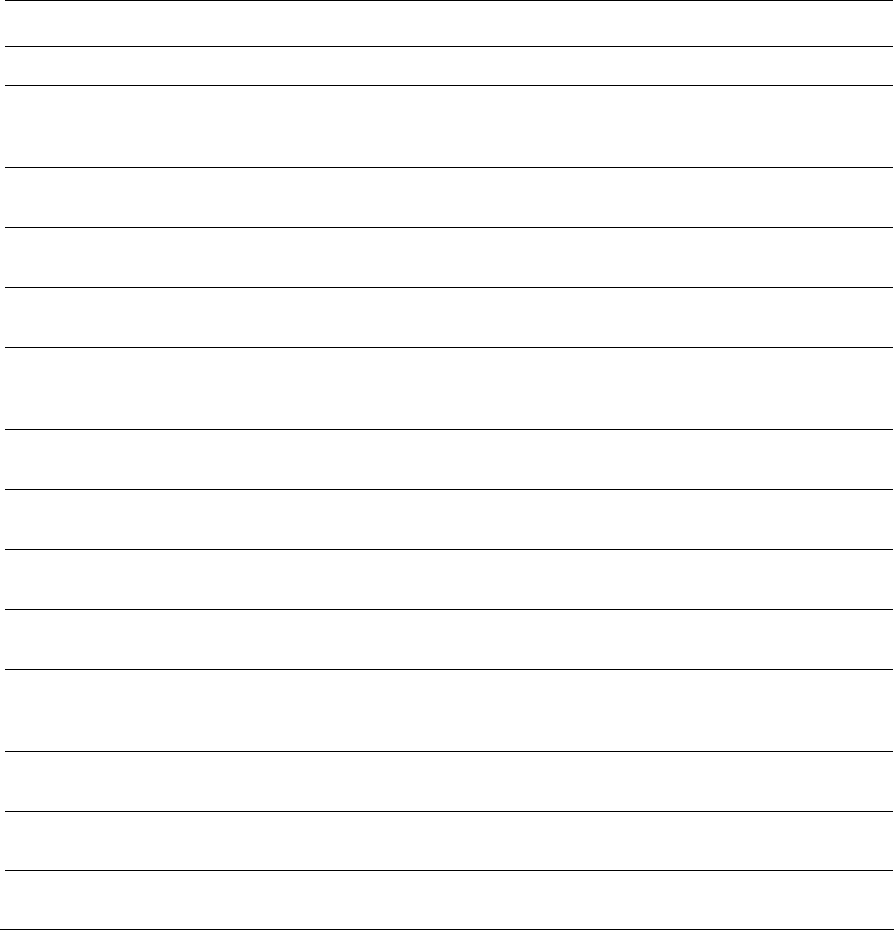

Table B-5 ARM926EJ-S PXP Development Chip bus timing

Bus signals Clock tov toh tis tih

HRESETn input XTALCLKEXT - - 10ns 2ns

AHB M1 outputs in synchronous mode (HADDR, HSELx,

HWRITE, HTRANS[1:0], HSIZE[2:0], HBURST[2:0], and

write data)

XTALCLKEXT 16ns 1ns - -

AHB M1 inputs in synchronous mode (HREADY, HRESP,

HLOCK, and read data)

XTALCLKEXT - - 17ns 0ns

AHB M1 outputs in async mode (HADDR, HSELx, HWRITE,

HTRANS[1:0], HSIZE[2:0], HBURST[2:0], and write data)

HCLKM1 18ns 4ns - -

AHB M1 inputs in async mode (HREADY, HRESP, HLOCK,

and read data)

HCLKM1 - - 17ns 4.5ns

AHB M2 outputs in synchronous mode (HADDR, HSELx,

HWRITE, HTRANS[1:0], HSIZE[2:0], HBURST[2:0], and

write data)

XTALCLKEXT 16ns 1ns - -

AHB M2 inputs in synchronous mode (HREADY, HRESP,

HLOCK, and read data)

XTALCLKEXT - - 17ns 0ns

AHB M2 outputs in async mode (HADDR, HSELx, HWRITE,

HSIZE[2:0], HBURST[2:0], and write data)

HCLKM2 18ns 4ns - -

AHB M2 inputs in async mode (HREADY, HRESP, HLOCK

,

and read data)

HCLKM2 - - 17ns 4.5ns

AHB S outputs in synchronous mode (HREADY, HRESP,

HLOCK, and read data)

XTALCLKEXT 16ns 1ns - -

AHB S inputs in synchronous mode (HADDR, HSELx,

HWRITE, HTRANS[1:0], HSIZE[2:0], HBURST[2:0], and

write data)

XTALCLKEXT - - 17ns 0ns

AHB S outputs in async mode (HREADY, HRESP, HLOCK,

and read data)

HCLKS 18ns 4ns - -

AHB S inputs in async mode (HADDR, HSELx, HWRITE,

HTRANS[1:0], HSIZE[2:0], HBURST[2:0], and write data)

HCLKS - - 17ns 4.5ns