Programmer’s Reference

4-72 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

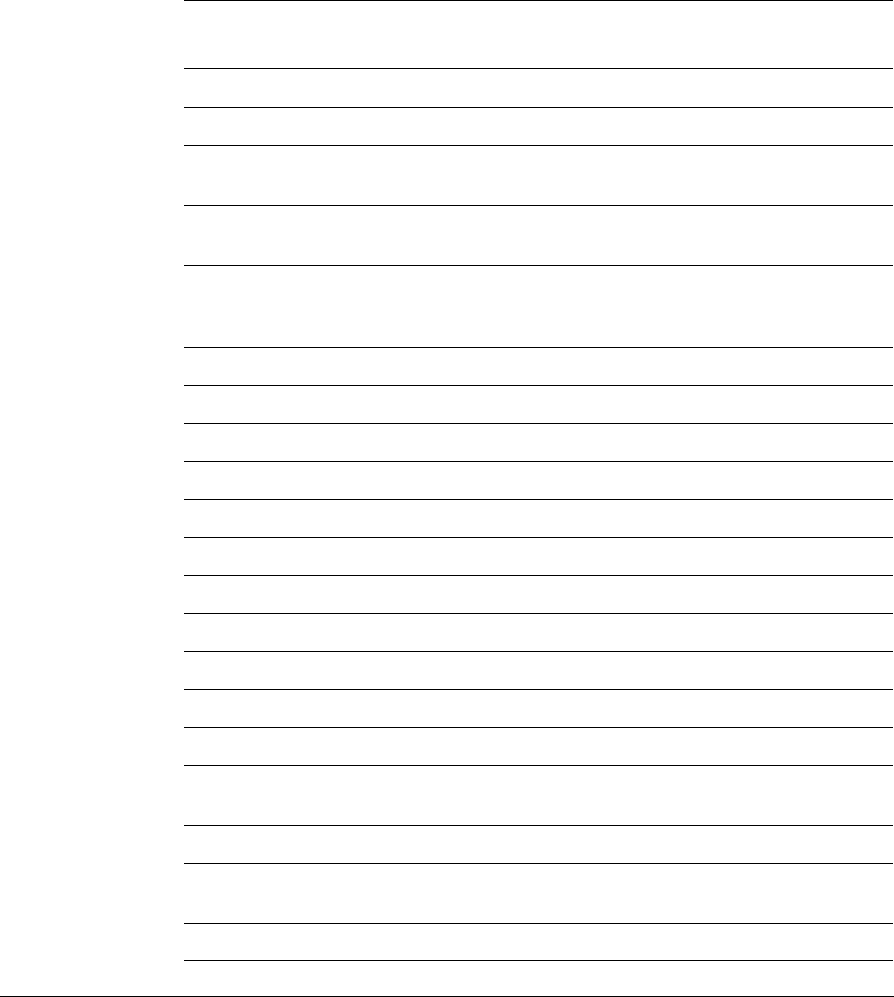

Table 4-47 SDRAM register values

Address

offset

Register name Value Description

+0x000 MPMCControl

0x1

Enabled

+0x008 MPMCConfig

0x0

Little Endian

+0x020 MPMCDynamicControl

0x3

MPMCCLKOUT runs

continuously, CKE high

+0x024 MPMCDynamicRefresh 0x22 544 cycles of HCLK between

refreshes

+0x028 MPMCDynamicReadConfig

0x111

command delayed strategy,

using MPMCCLKDELAY, data

capture on positive HCLK edge

+0x030 MPMCDynamictRP

0x2

42.86ns

+0x034 MPMCDynamictRAS

0x3

57.14ns

+0x038 MPMCDynamictSREX

0x5

85.71ns

+0x044 MPMCDynamictWR

0x4

71.43ns

+0x048 MPMCDynamictRC

0x5

85.71ns

+0x04c MPMCDynamictRFC

0x5

85.71ns

+0x050 MPMCDynamictXSR

0x5

85.71ns

+0x054 MPMCDynamictRRD

0x1

28.57ns

+0x058 MPMCDynamictMRD

0x2

42.86ns

+0x05c MPMCDynamictCDLR

0x1

28.57ns

+0x100 MPMCDynamicConfig0

0x5880

SDRAM32M16BRCX32

+0x104 MPMCDynamicRasCas0

0x202

CAS latency =2, RAS latency

=2

+0x120 MPMCDynamicConfig1

0x5880

SDRAM32M16BRCX32

+0x124 MPMCDynamicRasCas1

0x202

CAS latency =2, RAS latency

=2

+0x140 MPMCDynamicConfig2

0x5880

SDRAM32M16BRCX32