RealView Logic Tile

F-10 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

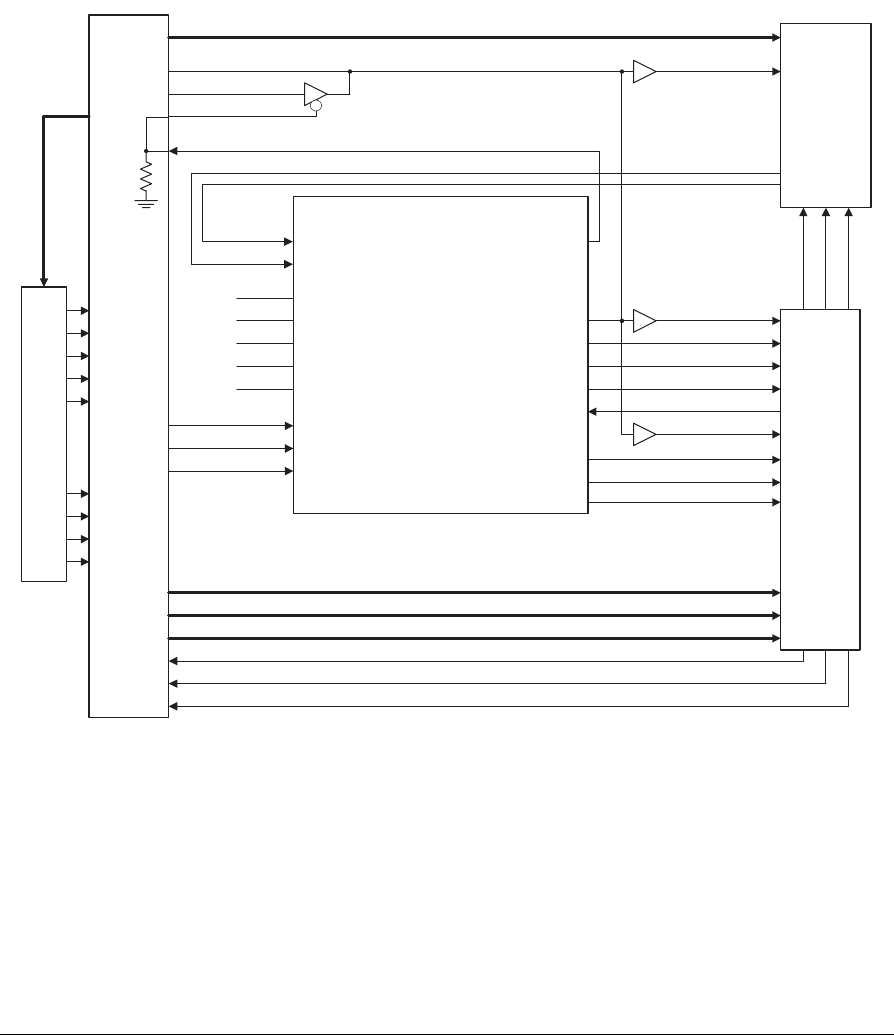

Figure F-5 Clock signals and the RealView Logic Tile

HCLKM1_L2S

HCLKM2_L2F

HCLKM1_L2F

HCLKM1F2L

HCLKM2F2L

HCLKSF2L

FPGA

ARM

926EJ-S

Dev.

Chip

Clock

select

circuit

HCLKx_X2S

XTALCLKDRV

HCLKM2_L2S

HCLKS_L2S

XTALCLKEXT

HCLKS_L2F

HCLKx_X2F

GLOBALCLK

HCLKS

HCLKM1

HCLKM2

HCLKSF

HCLKM1F

HCLKM2F

CLK_GLOBAL

XU131

XU132

XU133

XU128

XU129

XU130

CLK_POS_UP_OUT

ZU217

CLK_NEG_UP_OUT

CLK_NEG_DN_IN

NC

NC

CLK_POS_DN_IN

CLK_IN_PLUS1

NC

NC

CLK_IN_PLUS2

CLK_DN_THRU

NC

CLK_OUT_PLUS1

CLK_OUT_PLUS2

Logic Tile

HCLKCTRL[4:1]

HCLKxF2F

HCLKxF2S

SMCLK0

SMCLK1

HCLKCTRL0

xCLKEXT external clocks for dev. chip peripherals

Clock generators and crystals

ICS307 control

AHBMONCLK1

XU93

Z50

nGLOBALCLKEN