Programmer’s Reference

ARM DUI 0224F Copyright © 2003-2007 ARM Limited. All rights reserved. 4-31

4.3.9 Reset Control Register, SYS_RESETCTL

The SYS_RESETCTL register at

0x10000040

sets reset depth and programmable soft

reset, see Reset controller on page 3-22 and Reset level on page 3-24. The function of

the register bits are shown in Table 4-11. You must unlock the register (see Lock

Register, SYS_LOCK on page 4-24) before the register contents can be modified.

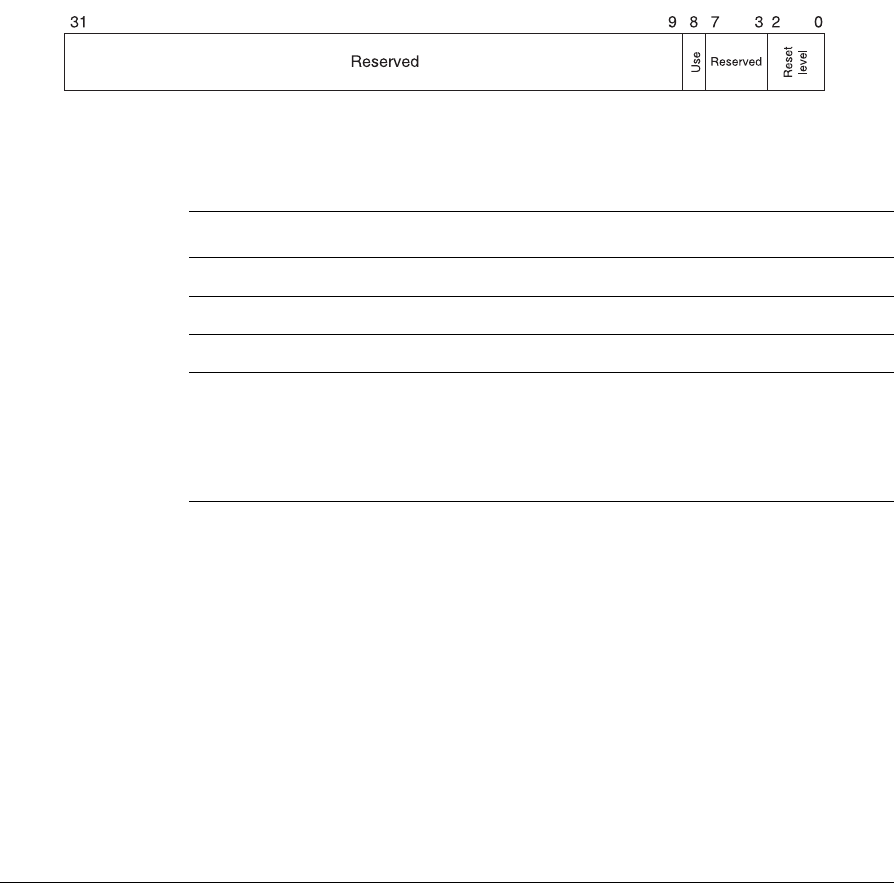

Figure 4-13 SYS_RESETCTL

4.3.10 PCI Control Register, SYS_PCICTL

The SYS_PCICTL register at

0x10000044

enables the bridge to the PCI bus:

• Setting bit 0 HIGH enables PCI bus accesses.

• Read returns a HIGH in bit 0 if a PCI board is present in the expansion backplane.

See Appendix D PCI Backplane and Enclosure, PCI controller on page 4-74, and PCI

interface on page 3-79 for more information on the PCI backplane.

4.3.11 MCI Register, SYS_MCI

The SYS_MCI register at

0x10000048

provides status information on the Multimedia

card sockets. The function of the register bits are shown in Table 4-12 on page 4-32.

Table 4-11 Reset level control

Bits Access Description

[31:9] Read write Reserved. Use read-modify-write to preserve value.

[8] Write Set this bit to generate a reset at the level specified by bits [2:0]

[7:3] Read write Reserved. Use read-modify-write to preserve value.

[2:0] Read write Select reset level:

b001–b000

resets to level 1, CONFIGCLR

b010

resets to level 2,

CONFIGINIT

b011

resets to level 3, DLLRESET

b100

resets to

level 4, PLLRESET

b101

resets to level 5, PORRESET

b111–b111

resets to level 6, DOCRESET