Memory Expansion Boards

E-16 Copyright © 2003-2007 ARM Limited. All rights reserved. ARM DUI 0224F

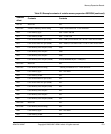

97 DQM[1], data mask input to

SDRAMs

98 NC

99 DQM[2], data mask input to

SDRAMs

100 NC

101 DQM[3], data mask input to

SDRAMs

102 NC

103 nRAS 104 NC

105 nCAS 106 NC

107 nWE 108 NC

109 nDYCS[0], SDRAM chip select 110 CKE[2], clock enable

111 nDYCS[1], SDRAM chip select 112 CKE[3], clock enable

113 nDYCS[2], SDRAM chip select 114 nRPOUT, SyncFlash reset power

down

115 nDYCS[3], SDRAM chip select 116 RPVHHOUT, Voltage control for

Micro SyncFlash reset signal

117 CKE[0], clock enable 118 CLK[2], clock out

119 CKE[1], clock enable 120 CLK[3], clock out

a. VDDIO is the I/O voltage to host. This is not routed through on stackable boards.

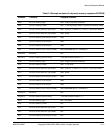

Table E-6 Static memory connector signals

Pin No. Signal Pin No. Signal

1 DATA[0] 2 3V3

3 DATA[1] 4 3V3

5 DATA[2] 6 3V3

7 DATA[3] 8 3V3

9 DATA[4] 10

VDDIO

a

11 DATA[5] 12

VDDIO

a

13 DATA[6] 14

VDDIO

a

Table E-5 SDR, Single data rate dynamic memory connector signals (continued)

Pin No. Signal Pin No. Signal