Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

102 Order Number: 252480-006US

3.6.10 Receive Register

(RX)

The RX register is the receive buffer used by the debug handler to get data sent by the

debugger through the JTAG interface.

Since the RX register is accessed by the debug handler (using MRC) and the debugger

(through JTAG), handshaking is required to prevent the debugger from writing new

data to the register before the debug handler reads the previous data out. The

handshaking is described in “RX Register Ready Bit (RR)” on page 99.

3.6.11 Debug JTAG Access

There are four JTAG instructions used by the debugger during software debug: LDIC,

SELDCSR, DBGTX and DBGRX. LDIC is described in “Downloading Code in ICache” on

page 116. The other three JTAG instructions are described in this section.

SELDCSR, DBGTX and DBGRX use a common 36-bit shift register (DBG_SR). New data

is shifted in and captured data out through the DBG_SR. In the UPDATE_DR state, the

new data shifted into the appropriate data register.

3.6.11.1 SELDCSR JTAG Command

The ‘SELDCSR’ JTAG instruction selects the DCSR JTAG data register. The JTAG op code

is ‘01001’. When the SELDCSR JTAG instruction is in the JTAG instruction register, the

debugger can directly access the Debug Control and Status Register (DCSR). The

debugger can only modify certain bits through JTAG, but can read the entire register.

The SELDCSR instruction also allows the debugger to generate an external debug

break.

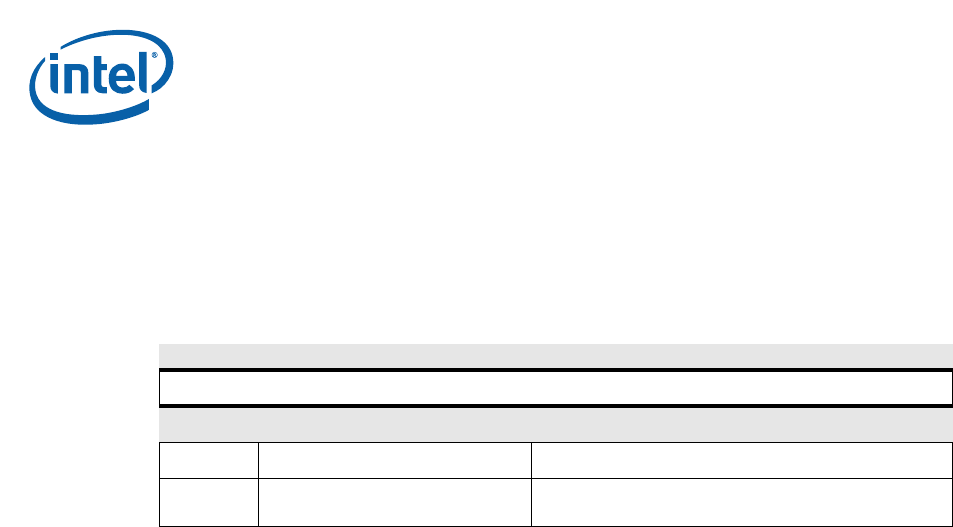

Table 44. RX Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RX

reset value: unpredictable

Bits Access Description

31:0

SW Read-only

JTAG Write-only

Software reads to receives data/commands from

debugger