Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 263

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

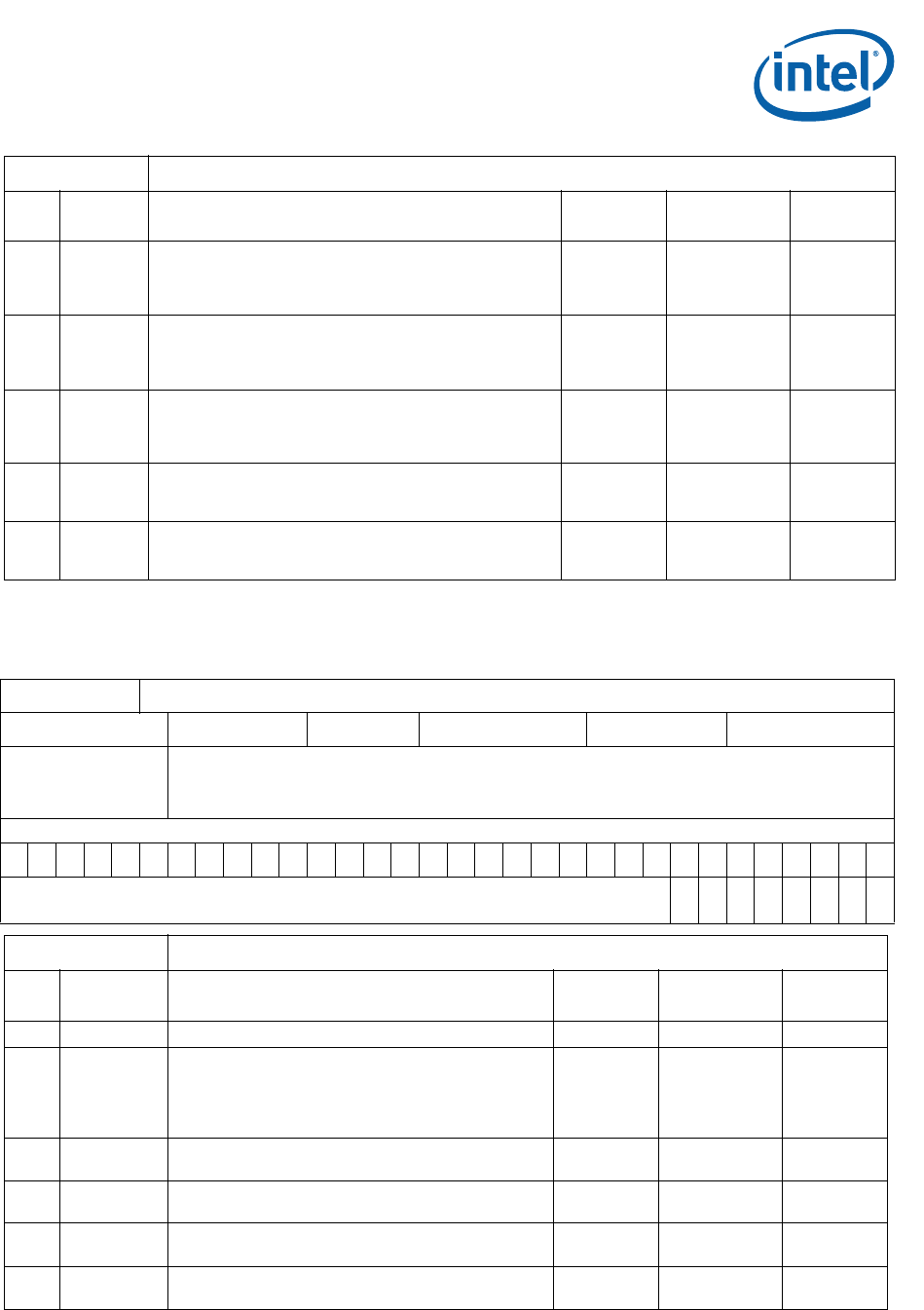

6.14.2.9 PCI Controller Interrupt Status Register

(PCI_ISR)

4ABE

AHB big-endian addressing. When 0, little-endian

addressing is employed on both AHB master and slave

interfaces. When 1, big-endian addressing is

implemented.

0RORW

3PDS

PCI byte swap. Controls byte lane data routing between

PCI and AHB buses during PCI Target accesses of the AHB

bus. When 1, byte lane swapping is performed. When 0,

no swapping is done.

0RORW

2ADS

AHB byte swap. Controls byte lane data routing between

PCI and AHB buses during AHB Slave accesses of the PCI

bus. When 1, byte lane swapping is performed. When 0,

no swapping is done.

0RORW

1ARBEN

Arbiter enable status. Indicates the state of the Expansion

bus address input bit corresponding to the PCI arbiter

setting at the de-assertion of reset_n.

0 or 1 RO RO

0HOST

Host status. Indicates the state of the Expansion bus

address input bit corresponding to the PCI host/option

setting at the deassertion of reset_n

0 or 1 RO RO

Register Name: PCI_ISR

Hex Offset Address: 0xC0000020 Reset Hex Value: 0x00000000

Register

Description:

Indicates the interrupt source(s) for the pcc_int interrupt output and the PCI interrupt PCI_INTA_N. With

the exception of PDB (PCI Doorbell), when any bit is a 1 and the corresponding bit in the pci_inten

register is set, pcc_int will be asserted. If the PDB bit is a 1 and the pci_inten.PDB bit is set, the

PCI_INTA_N output will be asserted to generate an interrupt on the PCI bus.

Access: See below.

31 876543210

(Reserved)

PDB

ADB

PADC

APDC

AHBE

PPE

PFE

PSE

Register PCI_ISR (Sheet 1 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access

31:8 (Reserved) – Read as 0 0x000000 RO RO

7PDB

PCI Doorbell interrupt. Asserted high when any one of

the bits in the pci_pcidoorbell register is set. This bit

does not cause an interrupt to be asserted on pcc_int.

When the pci_inten.PDB bit is set, the PCI_INTA_N

PCI interrupt output is asserted.

0RORO

6ADB

AHB Doorbell interrupt. Asserted high when any one

of the bits in the pci_ahbdoorbell register is set.

0RORO

5PADC

PCI to AHB DMA Complete. Asserted high when a PCI

to AHB DMA transfer is complete.

0RORO

4APDC

AHB to PCI DMA Complete. Asserted high when a AHB

to PCI DMA transfer is complete.

0RORO

3AHBE

AHB Error indication. Set to a 1 when the AHB Master

Interface receives an ERROR response.

0RORW1C

Register

PCI_CSR (Sheet 2 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access