Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 539

UTOPIA Level-2—Intel

®

IXP42X product line and IXC1100 control plane processors

When operating in single-PHY (SPHY) mode, the UTOPIA Level-2 interface will support

octet- or cell-level handshaking as defined by the UTOPIA Level-2 specification. When

configured in multiple-PHY (MPHY) mode, only cell-level handshaking is supported.

The hardware interface allows connection of up to 31 physical interface devices, as

defined in the UTOPIA Level-2 specification. However, the ATM Adaptation Layers (AAL)

supports only the following number of physical devices:

•Intel

®

IXP425 Network Processor — 24 physical devices

•Intel

®

IXP423 Network Processor — 4 physical devices

•Intel

®

IXP421 Network Processor — 4 physical devices

Additionally, the two-cycle polling routine defined by the UTOPIA Level-2 specification

limits the number of physical devices to 26.

The ATM Adaptation Layers (AAL) implemented by the Network Processor Engine may

have some further limitations on the number of physical interfaces supported. For more

details on the number of physical interfaces supported, see the Intel

®

IXP400 Software

Programmer’s Guide.

On the Network Processor Engine side of the UTOPIA-2 coprocessor, the UTOPIA-2

coprocessor interfaces to the Network Processor Engine Core via the Network Processor

Engine Coprocessor Bus Interface. The Network Processor Engine Coprocessor Bus

Interface is used to transfer data to and from the Network Processor Engine core. The

Network Processor Engine Coprocessor Bus Interface also is used to access status and

configuration information for the UTOPIA-2 coprocessor.

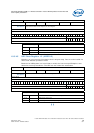

Figure 97 shows the various modules within the UTOPIA-2 coprocessor.