Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

212 Order Number: 252480-006US

pre-fetch CSR mechanism. Refer to “PCI Controller Configured as Host” on

page 213 for additional details.

For PCI bus memory cycles, the PCI Initiator interface will receive requests for PCI

transfer from the PCI Controller DMA channels. For PCI bus I/O cycles and configuration

cycles, the PCI Initiator interface will receive requests for PCI transfer from an AHB

master (a single word PCI Bus Memory Cycle can be produced using this method).

Requests for PCI transfers using the PCI Controller Initiator interface are buffered in

the Initiator Request FIFO and handled by the PCI Controller Initiator interface when

appropriate. The Initiator interface will receive the appropriate transfer information

from the Initiator Request FIFO; which is the address, word count, byte enables, and

PCI command type.

The Initiator Request FIFO is a four-entry FIFO allowing up to four requests to be

buffered. If a request is issued that generates an initiator transaction and the Initiator

Request FIFO is already full, a retry will be issued to the AHB master that initiated the

request.

After gathering the appropriate information, the PCI Initiator interface performs the

specified transaction on the PCI bus, handling all bus protocol and any retry/disconnect

situations. The data will be moved from the South AHB to the PCI bus using the

Initiator Data FIFOs. The Initiator Data FIFOs are eight words deep. Table 98 lists the

supported PCI transaction types produced by the IXP42X product line and IXC1100

control plane processors’ PCI Controller Initiator Interface.

It is important to note that the target interface — and the DMA channels used for

supporting the initiator interface — can contend for the use of the South AHB Master

Controller. When this contention occurs, arbitration for control of South AHB Master

Controller is carried out on two levels.

On the first level, the PCI Target Interface requests and the DMA requests alternate for

priority access. On the first transaction the PCI Target interface would gain access to

the South AHB Master Controller’s services, followed by one of the DMA channels

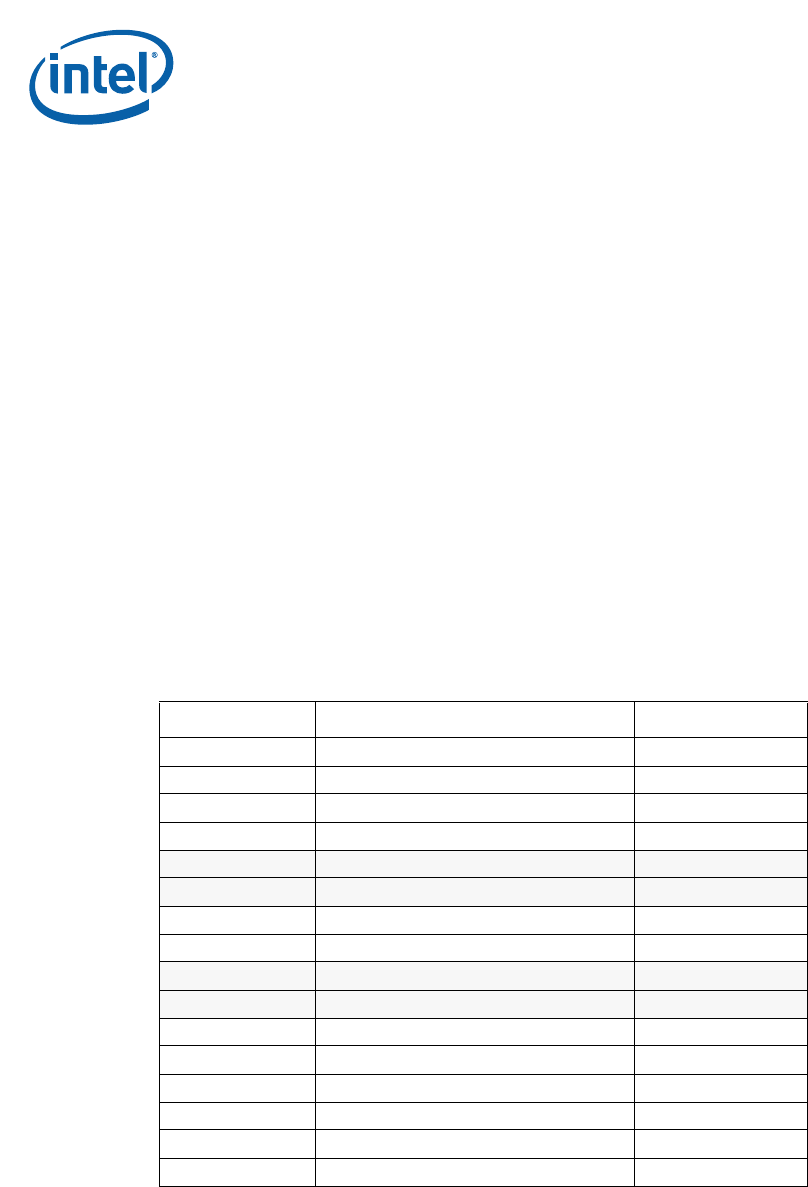

Table 98. PCI Initiator Interface-Supported Commands

PCI Byte Enables Command Type Support

0x0 Interrupt Acknowledge Supported

0x1 Special Cycle Supported

0x2 I/O Read Supported

0x3 I/O Write Supported

0x4 (Reserved)

0x5 (Reserved)

0x6 Memory Read Supported

0x7 Memory Write Supported

0x8 (Reserved)

0x9 (Reserved)

0xA Configuration Read Supported

0xB Configuration Write Supported

0xC Memory Read Multiple Not supported

0xD Dual Address Cycle Not supported

0xE Memory Read Line Not supported

0xF Memory Write and Invalidate Not supported