Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 147

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

Two new fields were created for this format, acc and opcode_3. The acc field specifies

one of eight internal accumulators to operate on and opcode_3 defines the operation

for this format. The Intel XScale processor defines a single 40-bit accumulator referred

to as acc0; future implementations may define multiple internal accumulators. The

Intel XScale processor uses opcode_3 to define six instructions, MIA, MIAPH, MIABB,

MIABT, MIATB and MIATT.

The MIA instruction operates similarly to MLA except that the 40-bit accumulator is

used. MIA multiplies the signed value in register Rs (multiplier) by the signed value in

register Rm (multiplicand) and then adds the result to the 40-bit accumulator (acc0).

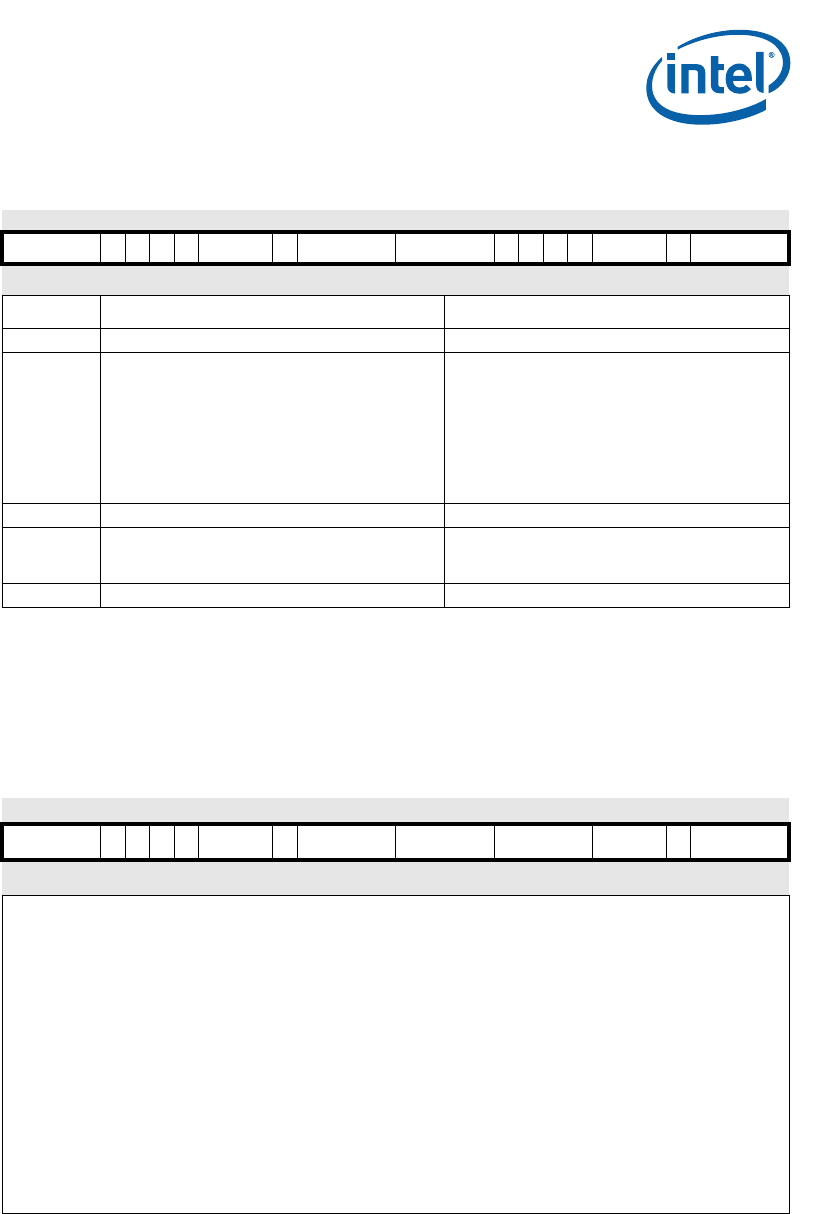

Table 62. Multiply with Internal Accumulate Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 11100010 opcode_3 Rs 0000 acc 1 Rm

Bits Description Notes

31:28 cond - ARM condition codes -

19:16

opcode_3 - specifies the type of multiply with

internal accumulate

Intel XScale processor defines the following:

0b0000 =

MIA

0b1000 = MIAPH

0b1100 = MIABB

0b1101 = MIABT

0b1110 = MIATB

0b1111 = MIATT

The effect of all other encodings are

unpredictable.

15:12 Rs - Multiplier

7:5 acc - select 1 of 8 accumulators

Intel XScale processor only implements acc0;

access to any other acc has unpredictable

effect.

3:0 Rm - Multiplicand -

Table 63. MIA{<cond>} acc0, Rm, Rs

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 111000100000 Rs 00000001 Rm

Operation: if ConditionPassed(<cond>) then

acc0 = (Rm[31:0] * Rs[31:0])[39:0] + acc0[39:0]

Exceptions: none

Qualifiers Condition Code

No condition code flags are updated

Notes: Early termination is supported. Instruction timings can be found

in “Multiply Instruction Timings” on page 163.

Specifying R15 for register Rs or Rm has unpredictable results.

acc0 is defined to be 0b000 on Intel XScale processor.