Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 79

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.5.1.3 Register 2: Translation Table Base Register

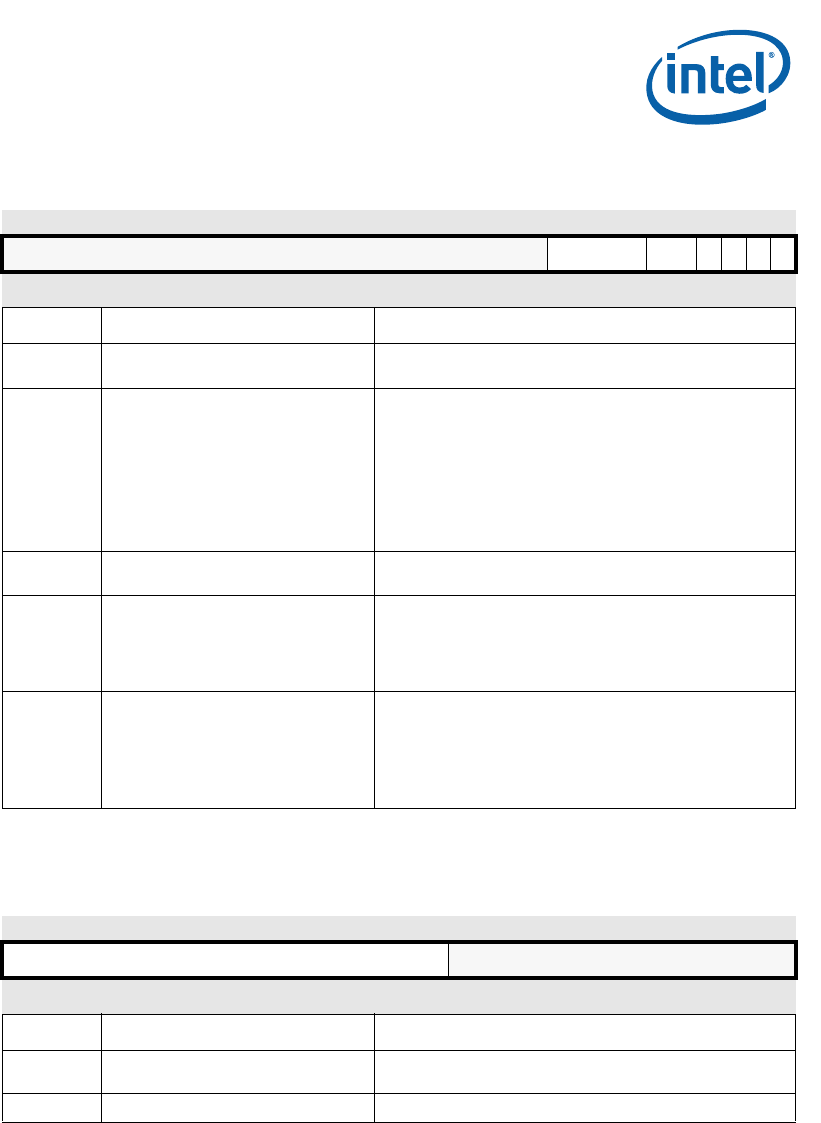

Table 13. Auxiliary Control Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PTEX MD C B P K

reset value: writeable bits set to 0

Bits Access Description

31:6

Read-Unpredictable /

Write-as-Zero

Reserved

5:4 Read / Write

Mini Data Cache Attributes (MD)

All configurations of the Mini-data cache are cacheable,

stores are buffered in the write buffer and stores will be

coalesced in the write buffer as long as coalescing is

globally enable (bit 0 of this register).

0b00 = Write back, Read allocate

0b01 = Write back, Read/Write allocate

0b10 = Write through, Read allocate

0b11 = Unpredictable

3:2

Read-Unpredictable/

Write-as-Zero

(Reserved)

1Read/Write

Page Table Memory Attribute (P)

This is a request to the core memory bus for a hardware

page table walk. An ASSP may use this bit to direct the

external bus controller to perform some special operation

on the memory access.

0Read / Write

Write Buffer Coalescing Disable (K)

This bit globally disables the coalescing of all stores in the

write buffer no matter what the value of the Cacheable

and Bufferable bits are in the page table descriptors.

0 = Enabled

1 = Disabled

Table 14. Translation Table Base Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Translation Table Base

reset value: unpredictable

Bits Access Description

31:14 Read / Write

Translation Table Base - Physical address of the base

of the first-level table

13:0 Read-unpredictable / Write-as-Zero Reserved