Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

106 Order Number: 252480-006US

A Capture_DR loads the TX register value into DBG_SR[34:3] and TXRXCTRL[28] into

DBG_SR[0]. The other bits in DBG_SR are loaded as shown in Figure 33.

The captured TX value is scanned out during the Shift_DR state.

Data scanned in is ignored on an Update_DR.

A ‘1’ captured in DBG_SR[0] indicates the captured TX data is valid. After doing a

Capture_DR, the debugger must place the JTAG state machine in the Shift_DR state to

guarantee that a debugger read clears TXRXCTRL[28].

3.6.11.5 DBGRX JTAG Command

The ‘DBGRX’ JTAG instruction selects the DBGRX JTAG data register. The JTAG op code

for this instruction is ‘0b00010’. Once the DBGRX data register is selected, the

debugger can send data to the debug handler through the RX register.

3.6.11.6 DBGRX JTAG Register

The DBGRX JTAG instruction selects the DBGRX JTAG Data register. The debugger uses

the DBGRX data register to send data or commands to the debug handler.

A Capture_DR loads TXRXCTRL[31] into DBG_SR[0]. The other bits in DBG_SR are

loaded as shown in Figure 18.

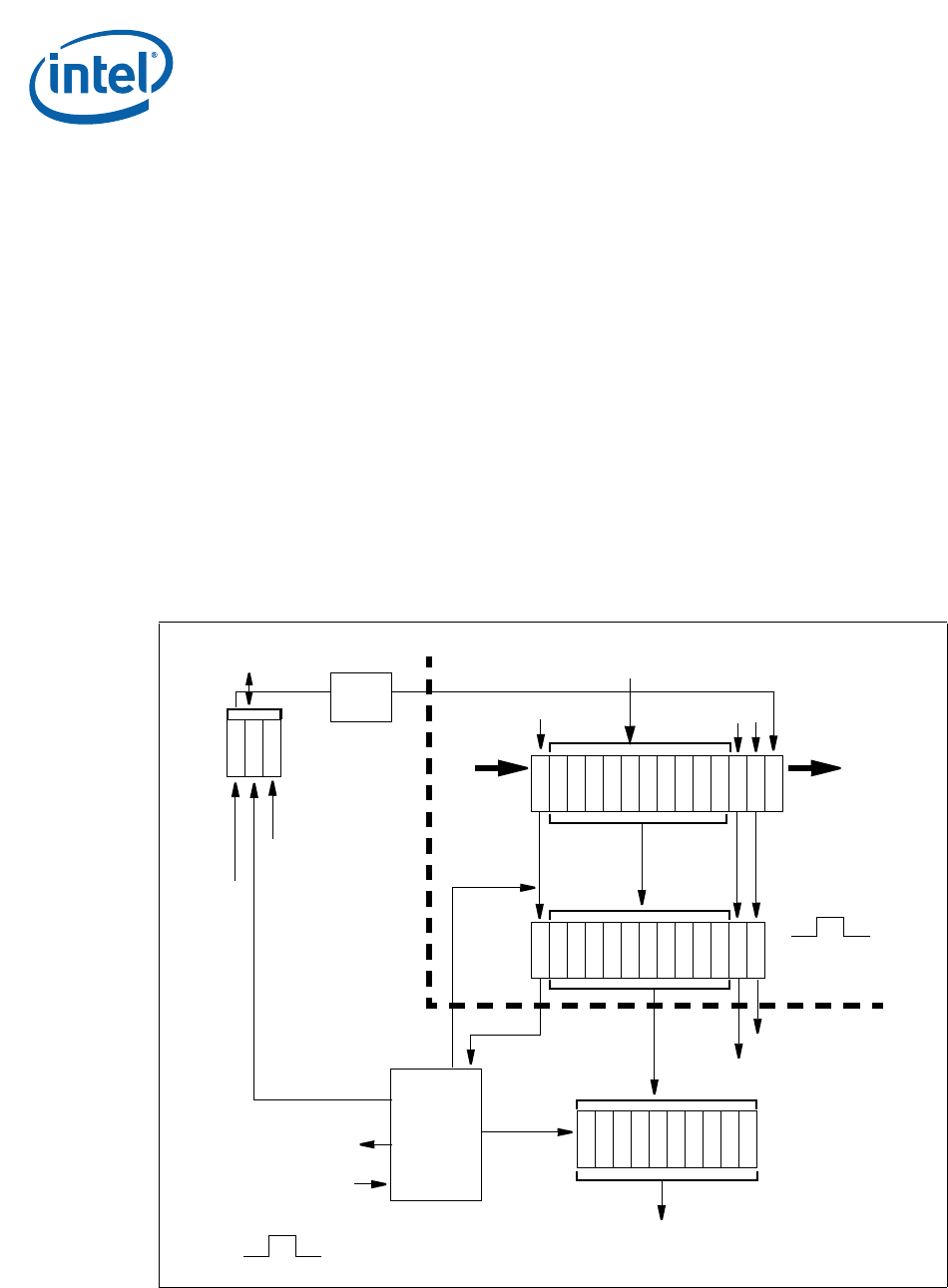

Figure 18. DBGRX Hardware

12

3334

TDOTDI

DBG_SR

Capture_DR

Update_DR

DBG_REG

123

3435

delay

031

software read

TXRXCTRL

RX

TCK

Core CLK

software read/write

0

0

0

0

1

3031 29

RX

DBG_REG[1]

Write

Logic

Flush RR

to TXRXCTRL[29]

TXRXCTRL[31]

set TXRXCTRL[31]

clear by SW read from RX

set by Debugger Write

clear DBG_REG[34]

undefined

enable

set overflow