Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 75

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.5.1 CP15 Registers

Table 9 lists the CP15 registers implemented in Intel

®

IXP42X Product Line of Network

Processors and IXC1100 Control Plane Processor.

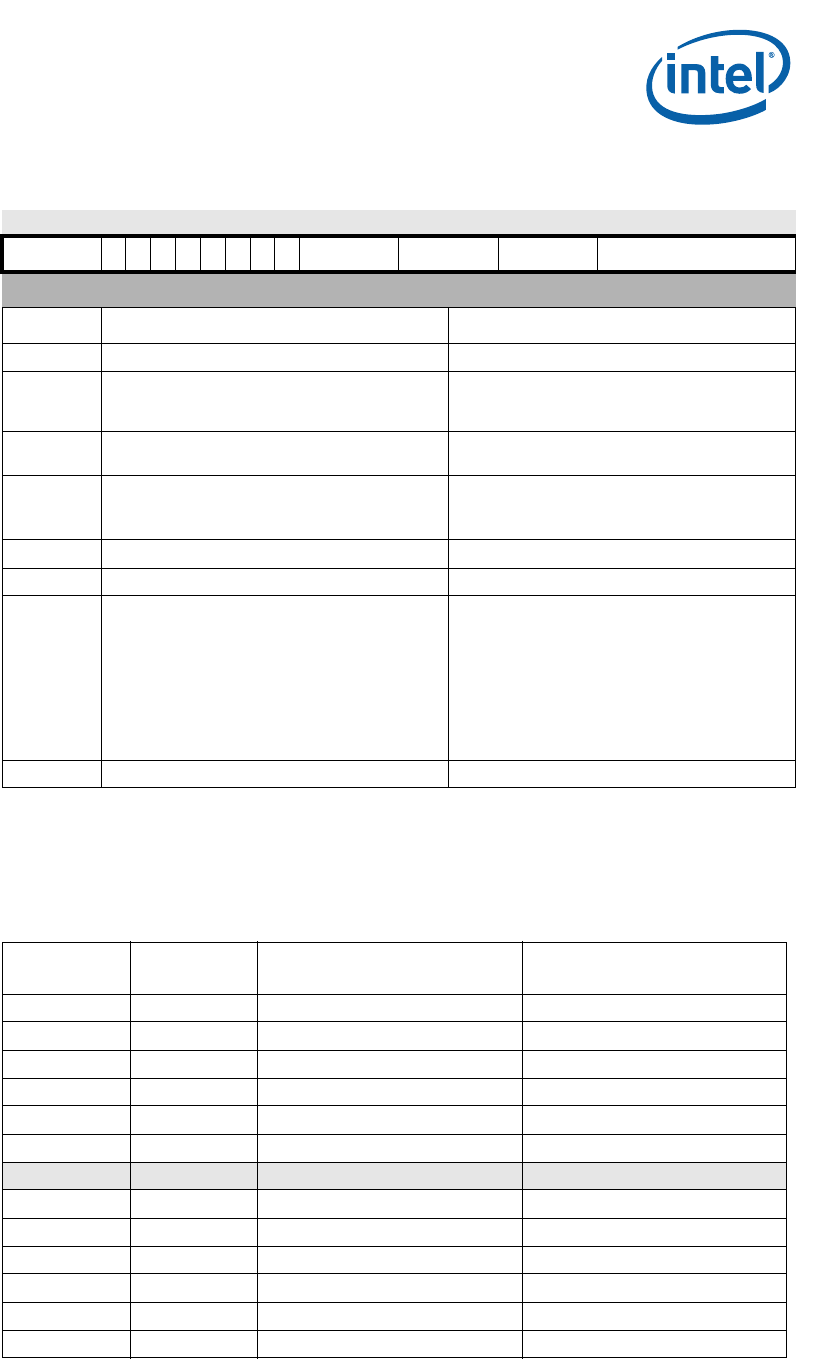

Table 8. LDC/STC Format when Accessing CP14

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1 1 0 P U N W L Rn CRd cp_num 8_bit_word_offset

Bits Description Notes

31:28 cond - ARM condition codes -

24:23,21

P, U, W - specifies 1 of 3 addressing modes

identified by addressing mode 5 in the ARM*

Architecture Reference Manual.

-

22

N - should be 0 for CP14 coprocessors. Setting

this bit to 1 has will have an undefined effect.

20

L - Load or Store

0 = STC

1 = LDC

-

19:16 Rn - specifies the base register -

15:12 CRd - specifies the coprocessor register -

11:8 cp_num - coprocessor number

Intel XScale processor defines the following:

0b1111 = Undefined Exception

0b1110 = CP14

Note: Mappings are implementation defined

for all coprocessors below CP13.

Access to unimplemented

coprocessors (as defined by the

cpConfig bus) cause exceptions.

7:0 8-bit word offset -

Table 9. CP15 Registers (Sheet 1 of 2)

Register

(CRn)

Opcode_2 Access Description

0 0 Read / Write-Ignored ID

0 1 Read / Write-Ignored Cache Type

1 0 Read / Write Control

1 1 Read / Write Auxiliary Control

20 Read / Write Translation Table Base

3 0 Read / Write Domain Access Control

4 - Unpredictable Reserved

5 0 Read / Write Fault Status

6 0 Read / Write Fault Address

7 0 Read-unpredictable / Write Cache Operations

8 0 Read-unpredictable / Write TLB Operations

9 0 Read / Write Cache Lock Down

10 0 Read-unpredictable / Write TLB Lock Down