Intel

®

IXP42X product line and IXC1100 control plane processors—Expansion Bus Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

304 Order Number: 252480-006US

The byte identification signal, EX_HBIL, is used to determine the byte transfer order.

(EX_HBIL is driven low for the first byte of the transfer and driven high for the second

byte.)

The byte order bit (BOB) in the HPIC register (contained in the DSP) — within the HPI

device — is used to determine the placement for the two bytes of the transfer. Please

consult the datasheet of the specific DSP being connected to determine the order of the

transferred bytes.

When operating in HPI mode, bits 13:10 in the Timing and Control (EXP_TIMING_CS)

Registers are ignored.

When operating in HPI-16, non-multiplexed mode, the expansion bus address bus

provides direct accesses to the DSP memory space. The data associated with this

address will be read or written from the location specified by the value contained on the

Expansion Bus address bits.

The signals EX_HCNTL [1:0] are multiplexed onto the EX_ADDR [2:1] pins. When

communicating to a multiplexed HPI interface, the EX_HCNTL [1:0] signals are used to

select one of four internal registers used for interfacing to the DSP. The EX_HCNTL

[1:0] mapping is described in the Table 121 below:

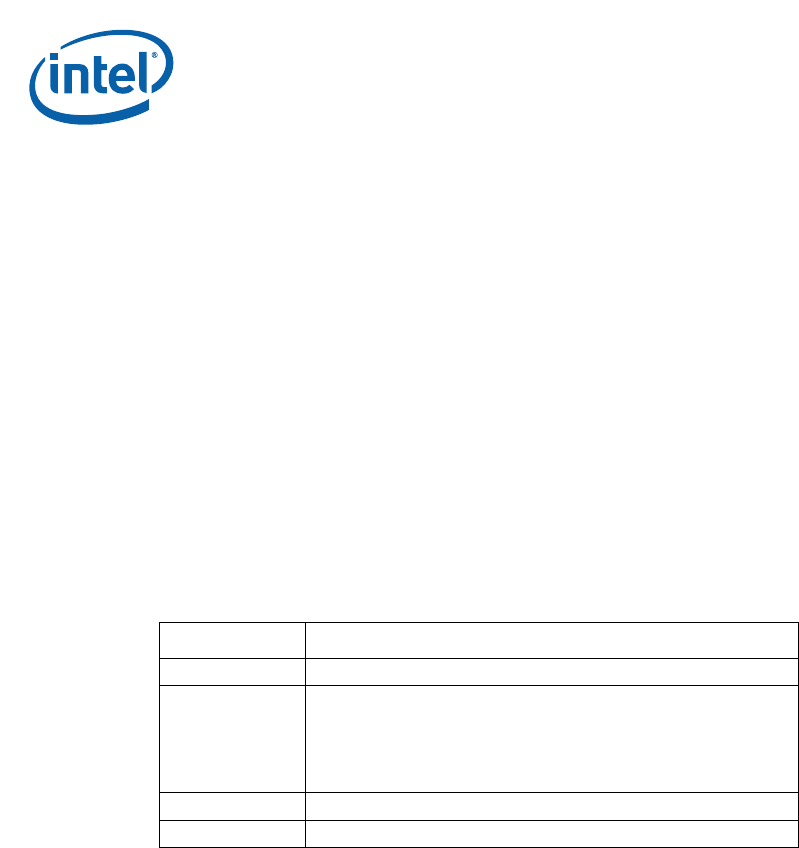

Table 121. HPI HCNTL Control Signal Decoding

hcntl[1:0] Required Access

00 Read / write control register (HPIC)

01

Read / write data register (HPID)

•HPI-8:

— Post-increment HPIA on reads, pre-increment on writes.

• HPI-16:

— Post-increment HPIA on reads and writes

10 Read / write address register (HPIA)

11 Read / write data register (HPID)