Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

150 Order Number: 252480-006US

Access to the internal accumulator is allowed in all processor modes (user and

privileged) as long bit 0 of the Coprocessor Access Register is set. (See “Register 15:

Coprocessor Access Register” on page 85 for more details).

The IXP42X product line and IXC1100 control plane processors implement two

instructions MAR and MRA that move two ARM registers to acc0 and move acc0 to two

ARM registers, respectively.

Note: MAR has the same encoding as MCRR (to coprocessor 0) and MRA has the same

encoding as MRRC (to coprocessor 0). These instructions move 64-bits of data to/from

ARM registers from/to coprocessor registers. MCRR and MRRC are defined in ARM’s

DSP instruction set.

Disassemblers not aware of MAR and MRA will produce the following syntax:

MCRR{<cond>} p0, 0x0, RdLo, RdHi, c0

MRRC{<cond>} p0, 0x0, RdLo, RdHi, c0

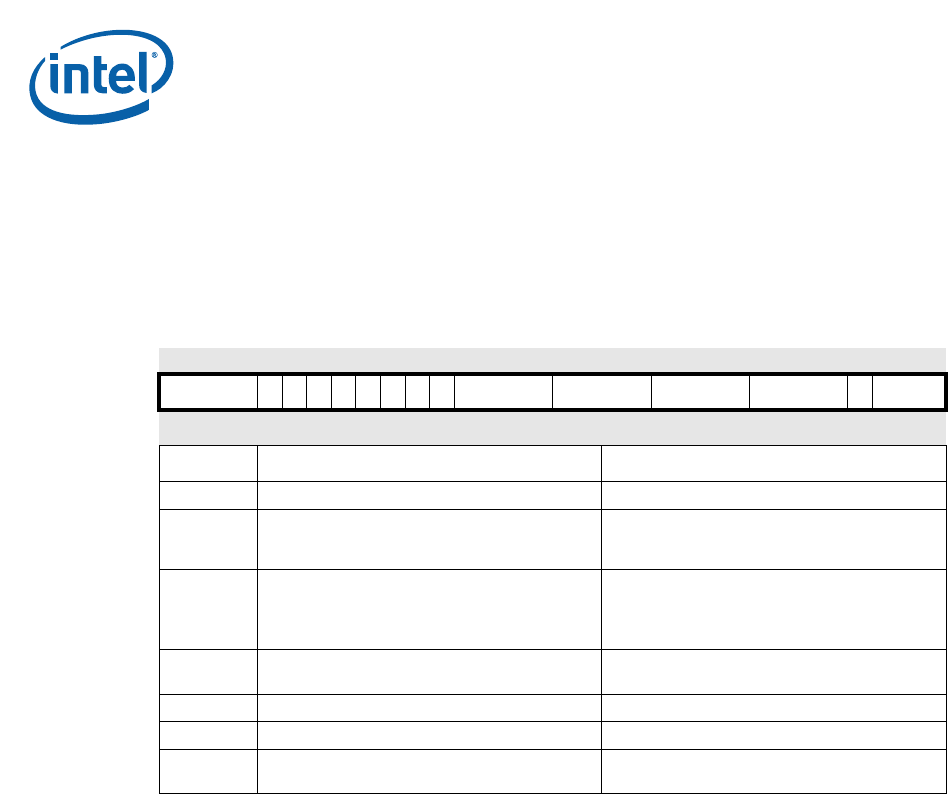

Table 66. Internal Accumulator Access Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1100010L RdHi RdLo 000000000 acc

Bits Description Notes

31:28 cond - ARM condition codes -

20

L - move to/from internal accumulator

0= move to internal accumulator (MAR)

1= move from internal accumulator (MRA)

-

19:16

RdHi - specifies the high order eight (39:32)

bits of the internal accumulator.

On a read of the acc, this 8-bit high order field

will be sign extended.

On a write to the acc, the lower 8 bits of this

register will be written to acc[39:32]

15:12

RdLo - specifies the low order 32 bits of the

internal accumulator

-

7:4 Should be zero

3 Should be zero -

2:0 acc - specifies 1 of 8 internal accumulators

Intel XScale processor only implements acc0;

access to any other acc is unpredictable