Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 221

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

— BAR4 = 0xA4000000

— BAR5 = 0xA5123400

3. An external PCI device initiates a PCI bus transfer to the IXP42X product line and

IXC1100 control plane processors’ BAR1. The PCI address looks like the following

PCI Address = 0xA100402C. The address placed on the South AHB is 0100402C.

Notice that the third byte from the right, of the PCI_AHBMEMBASE = 0x04010506,

is substituted for the A1 located in the fourth byte from the right of the PCI Address

= 0xA100402C.

4. Next, an external PCI device initiates a PCI bus transfer to the IXP42X product line

and IXC1100 control plane processors’ BAR3. The PCI address looks like the

following: PCI Address = 0xA3004014. The address placed on the South AHB is

06004014.

Notice that the first

byte from the right of the PCI_AHBMEMBASE = 0x04010506 is

substituted for the A3 located in the fourth byte from the right of the PCI Address =

0xA3004014.

5. PCI I/O space example is an external PCI device initiates a PCI bus transfer to the

IXP42X product line and IXC1100 control plane processors’ BAR5. The PCI address

looks like the following PCI Address = 0xA5123418. The address placed on the

South AHB is 0x0A120018.

Notice that the first

three bytes from the right of the PCI_AHBIOBASE =

0x000A1200 is substituted for the A51234 located in the PCI Address =

0xA5123418.

6. The final example is an external PCI device initiates a PCI bus transfer to the

IXP42X product line and IXC1100 control plane processors’ BAR4. This allows

access to the PCI Controller Configuration and Status Register. The PCI address

looks like the following PCI Address = 0xA4000038. There is no address placed on

the South AHB. This causes an access of the PCI Doorbell Register on the IXP42X

product line and IXC1100 control plane processors.

The PCI Doorbell Register can be used to generate an interrupt to the Intel XScale

processor.

When the IXP42X product line and IXC1100 control plane processors are the initiator of

a PCI Bus transaction and desires the transaction to produce PCI Memory Transactions,

the values may be written or read by providing a transfer to the PCI Memory Cycle

Address Space defined for the IXP42X product line and IXC1100 control plane

processors. The 64-Mbyte address space defined for the PCI Memory Cycle Address

Space is from AHB address location 0x48000000 to 0x4BFFFFFF.

Only four 16-Mbyte windows can be enabled. The four 16-Mbyte windows are divided

among the addresses as shown in Table 99.

The four 16-Mbyte windows translate their South AHB addresses to the PCI Bus

addresses using the PCI Memory Base Address Register (PCI_PCIMEMBASE).

The PCI Memory Base Address Register (PCI_PCIMEMBASE) register consists of four 8-

bit fields. Each of these fields corresponds to a given 16-Mbyte window:

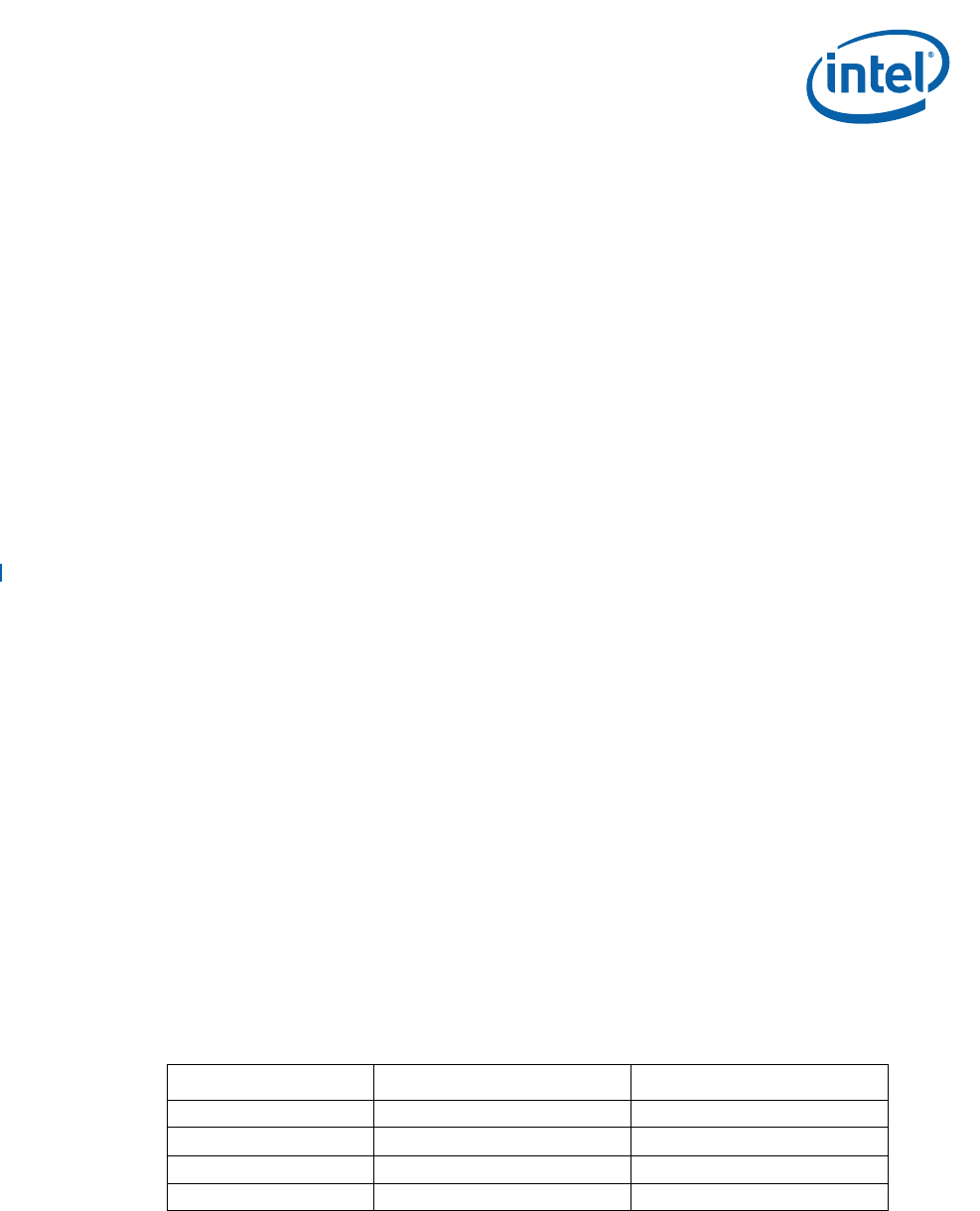

Table 99. PCI Memory Map Allocation

Description Starting Address Ending Address

First 16-Mbyte window 0x48000000 0x48FFFFFF

Second 16-Mbyte window 0x49000000 0x49FFFFFF

Third 16-Mbyte window 0x4A000000 0x4AFFFFFF

Fourth 16-Mbyte window 0x4B000000 0x4BFFFFFF