Intel

®

IXP42X product line and IXC1100 control plane processors—AHB Queue Manager (AQM)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

564 Order Number: 252480-006US

21.5.4 Queues 32-63 Nearly Empty Status Register

The access to these status registers is read/write, however except for diagnostic and

test purposes, normal operation to these registers should be read only. Writing status

does not actually change the status, it only writes the shadow register which contains

the status.

21.5.5 Queues 32-63 Full Status Register

The access to these status registers is read/write, however except for diagnostic and

test purposes, normal operation to these registers should be read only. Writing status

does not actually change the status, it only writes the shadow register which contains

the status.

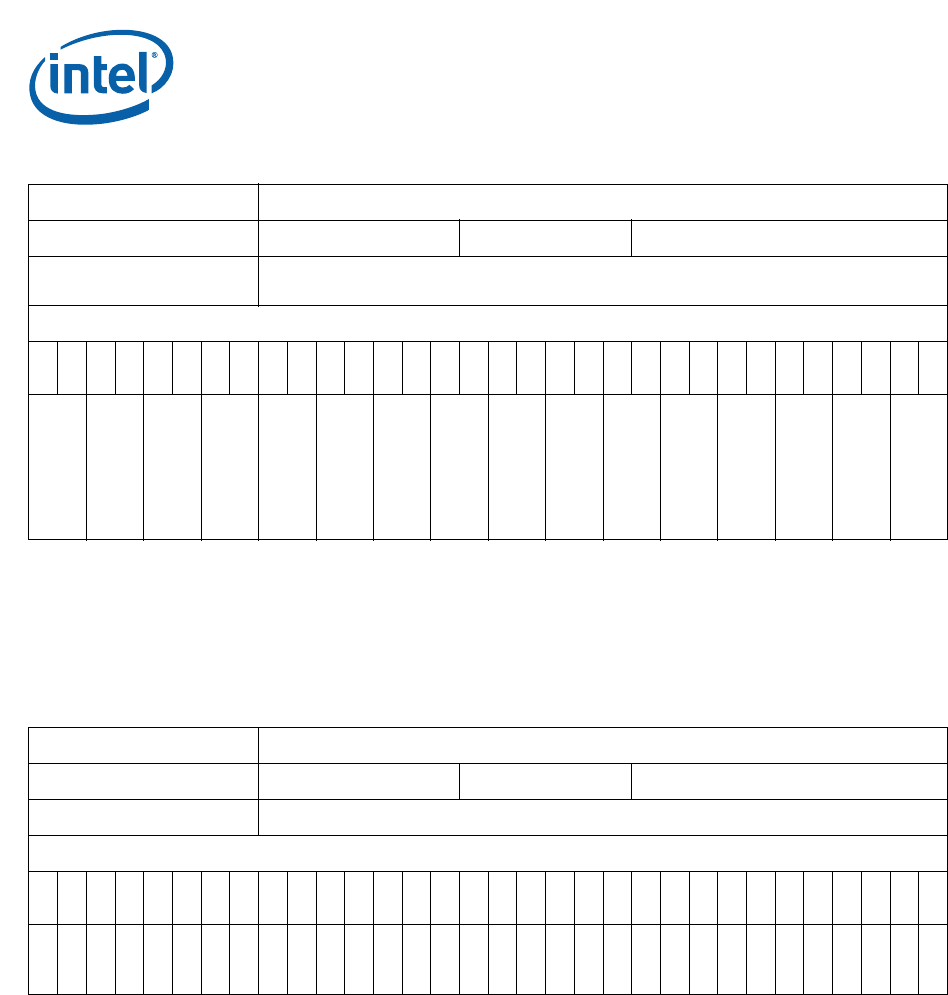

Register Name: QUEUOSTAT (0 <= n <=1)

Physical Address:

Queue #n 0x(0410 + 4n)

Reset Hex Value: 0x00000000

Register Description:

Queue underflow/overflow status register for the queues 0-31. OF/UF: ‘1’ – Overflow/Underflow

has occurred

Access: Read/Write

3

1

2

4

2

3

1

6

1

5

87 0

Queue (16n + 15)

Queue (16n + 14)

Queue (16n + 13)

Queue (16n + 12)

Queue (16n + 11)

Queue (16n + 10)

Queue (16n + 9)

Queue (16n + 8)

Queue (16n + 7)

Queue (16n + 6)

Queue (16n + 5)

Queue (16n + 4)

Queue (16n + 3)

Queue (16n + 2)

Queue (16n + 1)

Queue (16n)

Register Name: QUEUPPSTATNE

Physical Address:

0x0418

Reset Hex Value: 0xFFFFFFFF

Register Description: Queue status register for queues 32-63. NE: ‘1’ – flag set

Access: Read/Write

3

1

1

6

1

5

87 0

Q63 NE

Q62 NE

Q61 NE

Q60 NE

Q59 NE

Q58 NE

Q57 NE

Q56 NE

Q55 NE

Q54 NE

Q53 NE

Q52 NE

Q51 NE

Q50 NE

Q49 NE

Q48 NE

Q47 NE

Q46 NE

Q45 NE

Q44 NE

Q43 NE

Q42 NE

Q41 NE

Q40 NE

Q39 NE

Q38 NE

Q37 NE

Q36 NE

Q35 NE

Q34 NE

Q33 NE

Q32 NE