Intel

®

IXP42X product line and IXC1100 control plane processors—Ethernet MAC A

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

416 Order Number: 252480-006US

15.0 Ethernet MAC A

The functionality supported by the MII Interfaces is tightly coupled with the code

written on the Network Processor Engine (NPE) core. This chapter details the full

hardware capabilities of the MII Interface contained within the Ethernet coprocessor of

the Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane

Processor. The features accessible by the user are described in the Intel

®

IXP400

Software Programmer’s Guide and may be a subset of the features described below.

Not all of the Intel

®

IXP42X product line and IXC1100 control plane processors have

this functionality. See Table 151.

The IXP42X product line and IXC1100 control plane processors contains three NPEs.

Two of the three NPEs are used to process Ethernet traffic utilizing the MII interfaces.

Each NPE core used for Ethernet traffic connects to a Transmit FIFO and Receive FIFO

through the NPE Coprocessor interface. These Transmit and Receive FIFOs are used to

buffer data between the Ethernet Media Access Controller (MAC) and the NPE core.

The Transmit FIFO, Receive FIFO, and MAC are contained in an NPE coprocessor unit

called the Ethernet Coprocessor. The MAC contained in the Ethernet coprocessor is

compliant to the IEEE 802.3 specification as well as handling flow control for the

IEEE 802.3Q VLAN specification.

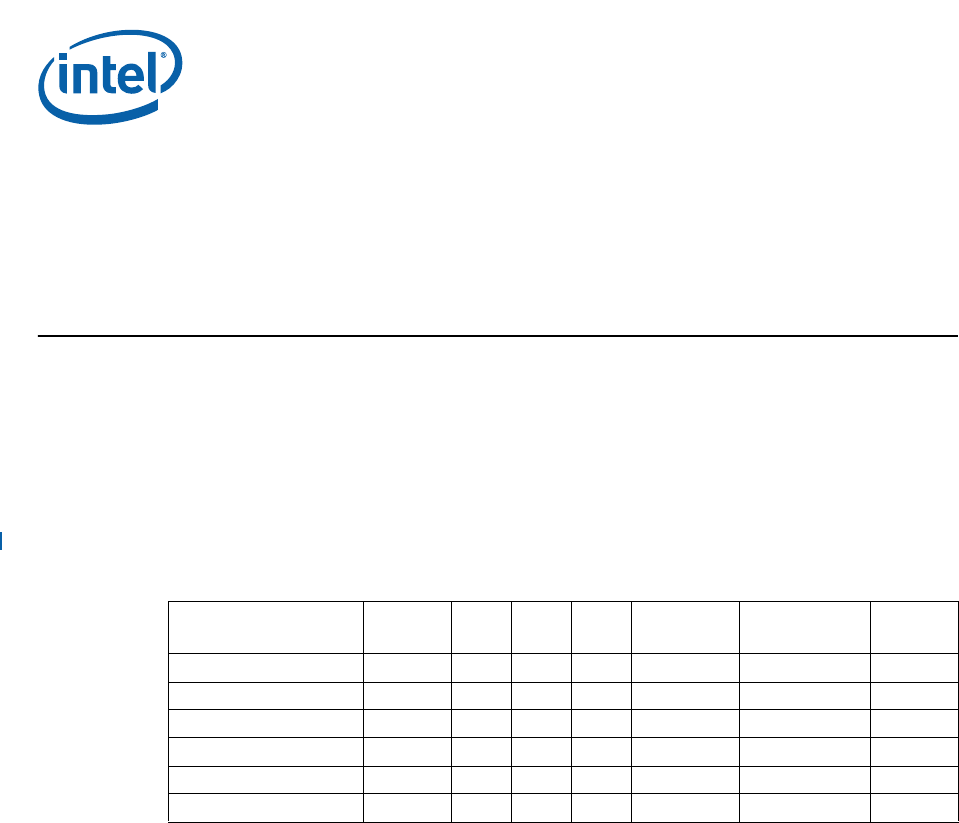

Table 151. Processors’ Devices with Ethernet Interface

Device UTOPIA HSS MII 0 MII 1

AES / DES /

3DES

Multi-Channel

HDLC

SHA-1 /

MD-5

IXP425 X X X X X 8 X

IXP423 X X X X 8

IXP422 X X X X

IXP421 X X X 8

IXP420 X X

IXC1100 X X