Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

118 Order Number: 252480-006US

3.6.14.3 LDIC Cache Functions

The IXP42X product line and IXC1100 control plane processors support four cache

functions that can be executed through JTAG. Two functions allow an external host to

download code into the main instruction cache or the mini instruction cache through

JTAG. Two additional functions are supported to allow lines to be invalidated in the

instruction cache. The following table shows the cache functions supported through

JTAG.

Invalidate IC line invalidates the line in the instruction cache containing specified virtual

address. If the line is not in the cache, the operation has no effect. It does not take any

data arguments.

Invalidate Mini IC will invalidate the entire mini instruction cache. It does not effect the

main instruction cache. It does not require a virtual address or any data arguments.

Note: The LDIC Invalidate Mini IC function does not invalidate the BTB (like the CP15

Invalidate IC function) so software must do this manually where appropriate.

Load Main IC and Load Mini IC write one line of data (eight ARM instructions) into the

specified instruction cache at the specified virtual address.

Each cache function is downloaded through JTAG in 33 bit packets. Figure 25 shows the

packet formats for each of the JTAG cache functions. Invalidate IC Line and Invalidate

Mini IC each require 1 packet. Load Main IC and Load Mini IC each require 9 packets.

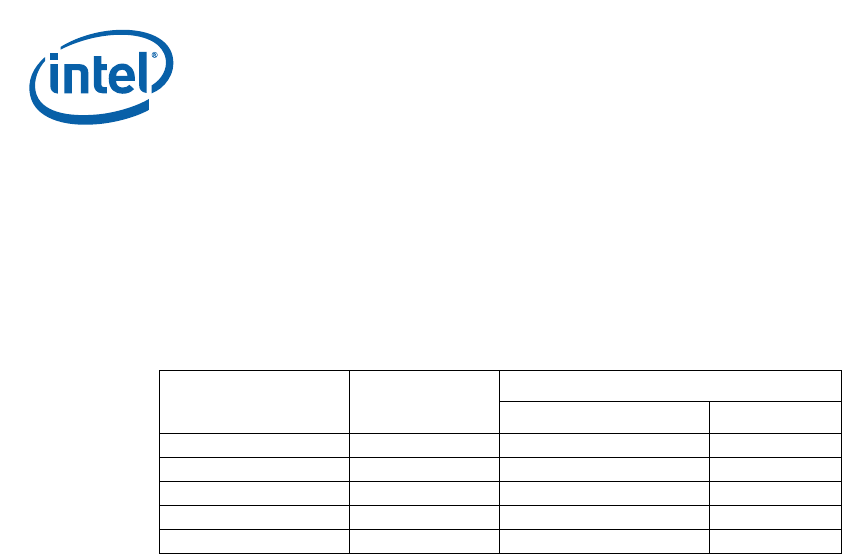

Table 50. LDIC Cache Functions

Function Encoding

Arguments

Address # Data Words

Invalidate IC Line 0b000 VA of line to invalidate 0

Invalidate Mini IC 0b001 - 0

Load Main IC 0b010 VA of line to load 8

Load Mini IC 0b011 VA of line to load 8

RESERVED 0b100-0b111 - -