Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 87

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.5.2.1 Performance Monitoring Registers

The performance monitoring unit contains a control register (PMNC), a clock counter

(CCNT), interrupt enable register (INTEN), overflow flag register (FLAG), event

selection register (EVTSEL) and four event counters (PMN0 through PMN3). The format

of these registers can be found in “Performance Monitoring” on page 133, along with a

description on how to use the performance monitoring facility.

Opcode_2 should be zero on all accesses.

These registers can’t be accessed by LDC and STC coprocessor instructions.

3.5.2.2 Clock and Power Management Registers

These registers contain functions for managing the core clock and power.

For the IXP42X product line and IXC1100 control plane processors, these registers are

not implemented and reserved for future use.

The Intel XScale processor clock frequency cannot be changed by software on the

IXP42X product line and IXC1100 control plane processors.

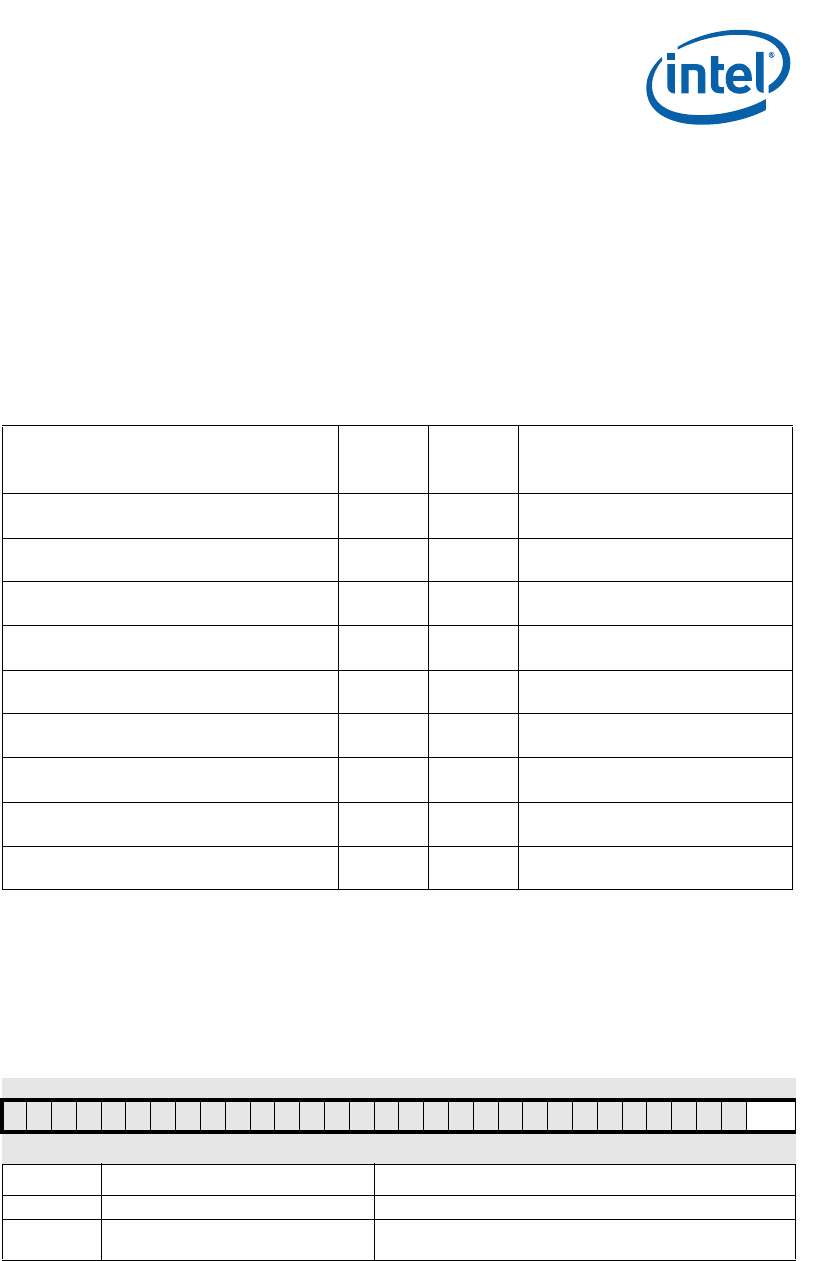

Table 28. Accessing the Performance Monitoring Registers

Description

CRn

Register

#

CRm

Register

#

Instruction

(PMNC) Performance Monitor Control

Register

0b0000 0b0001

Read: MRC p14, 0, Rd, c0, c1, 0

Write: MCR p14, 0, Rd, c0, c1, 0

(CCNT) Clock Counter Register 0b0001 0b0001

Read: MRC p14, 0, Rd, c1, c1, 0

Write: MCR p14, 0, Rd, c1, c1, 0

(INTEN) Interrupt Enable Register 0b0100 0b0001

Read: MRC p14, 0, Rd, c4, c1, 0

Write: MCR p14, 0, Rd, c4, c1, 0

(FLAG) Overflow Flag Register 0b0101 0b0001

Read: MRC p14, 0, Rd, c5, c1, 0

Write: MCR p14, 0, Rd, c5, c1, 0

(EVTSEL) Event Selection Register 0b1000 0b0001

Read: MRC p14, 0, Rd, c8, c1, 0

Write: MCR p14, 0, Rd, c8, c1, 0

(PMN0) Performance Count Register 0 0b0000 0b0010

Read: MRC p14, 0, Rd, c0, c2, 0

Write: MCR p14, 0, Rd, c0, c2, 0

(PMN1) Performance Count Register 1 0b0001 0b0010

Read: MRC p14, 0, Rd, c1, c2, 0

Write: MCR p14, 0, Rd, c1, c2, 0

(PMN2) Performance Count Register 2 0b0010 0b0010

Read: MRC p14, 0, Rd, c2, c2, 0

Write: MCR p14, 0, Rd, c2, c2, 0

(PMN3) Performance Count Register 3 0b0011 0b0010

Read: MRC p14, 0, Rd, c3, c2, 0

Write: MCR p14, 0, Rd, c3, c2, 0

Table 29. PWRMODE Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

M

reset value: writeable bits set to 0

Bits Access Description

31:0 Read-unpredictable / Write-as-Zero Reserved

1:0 Read / Write

Mode (M)

0 = ACTIVE Never change from 00b