Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

74 Order Number: 252480-006US

Unless otherwise noted, unused bits in coprocessor registers have unpredictable values

when read. For compatibility with future implementations, software should not rely on

the values in those bits.

The format of LDC and STC for CP14 is shown in Table 8. LDC and STC follow the

programming notes in the ARM* Architecture Reference Manual. Note that access to

CP15 with LDC and STC will cause an undefined exception.

LDC and STC transfer a single 32-bit word between a coprocessor register and

memory. These instructions do not allow the programmer to specify values for

opcode_1, opcode_2, or Rm; those fields implicitly contain zero, which means the

performance monitoring registers are not accessible.

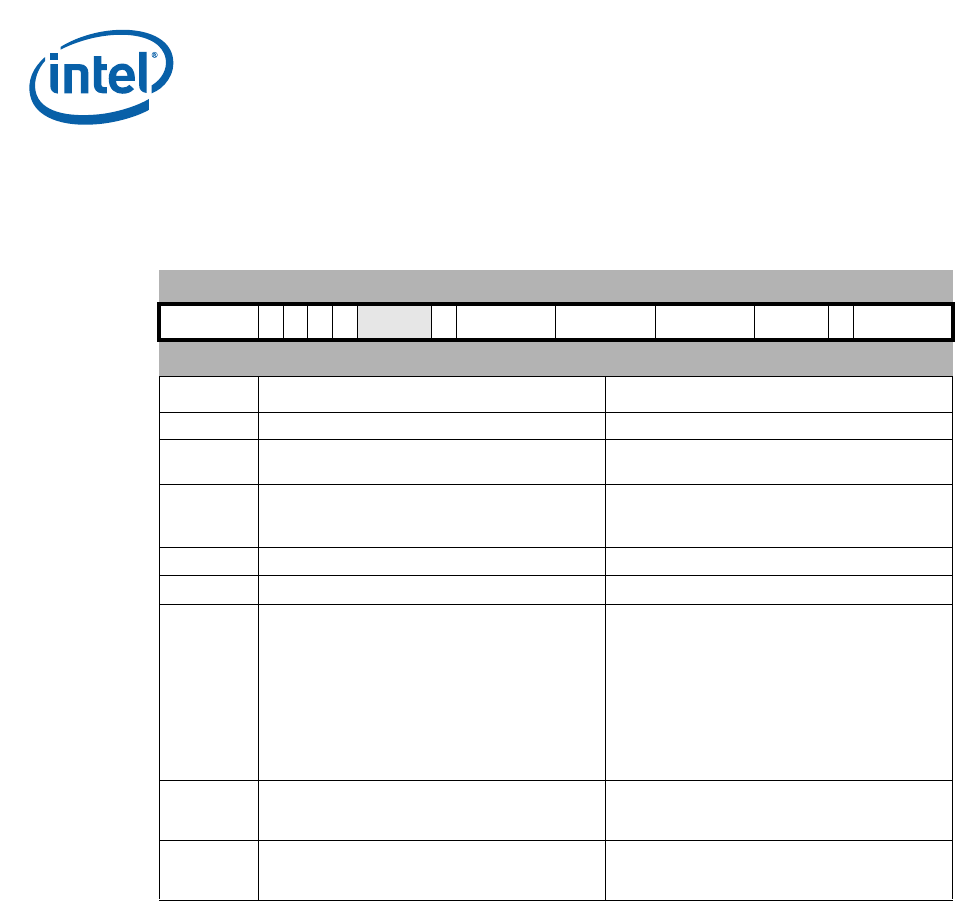

Table 7. MRC/MCR Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 1 1 1 0 opcode_1 n CRn Rd cp_num opcode_2 1CRm

Bits Description Notes

31:28 cond - ARM condition codes -

23:21 opcode_1 - Reserved

Should be programmed to zero for future

compatibility

20

n - Read or write coprocessor register

0 = MCR

1 = MRC

-

19:16 CRn - specifies which coprocessor register -

15:12 Rd - General Purpose Register, R0..R15 -

11:8 cp_num - coprocessor number

Intel XScale processor defines three

coprocessors:

0b1111 = CP15

0b1110 = CP14

0x0000 = CP0

Note: Mappings are implementation defined

for all coprocessors below CP14 and

above CP0. Access to unimplemented

coprocessors (as defined by the

cpConfig bus) cause exceptions.

7:5 opcode_2 - Function bits

This field should be programmed to zero for

future compatibility unless a value has been

specified in the command.

3:0 CRm - Function bits

This field should be programmed to zero for

future compatibility unless a value has been

specified in the command.