Intel

®

IXP42X product line and IXC1100 control plane processors—Ethernet MAC A

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

428 Order Number: 252480-006US

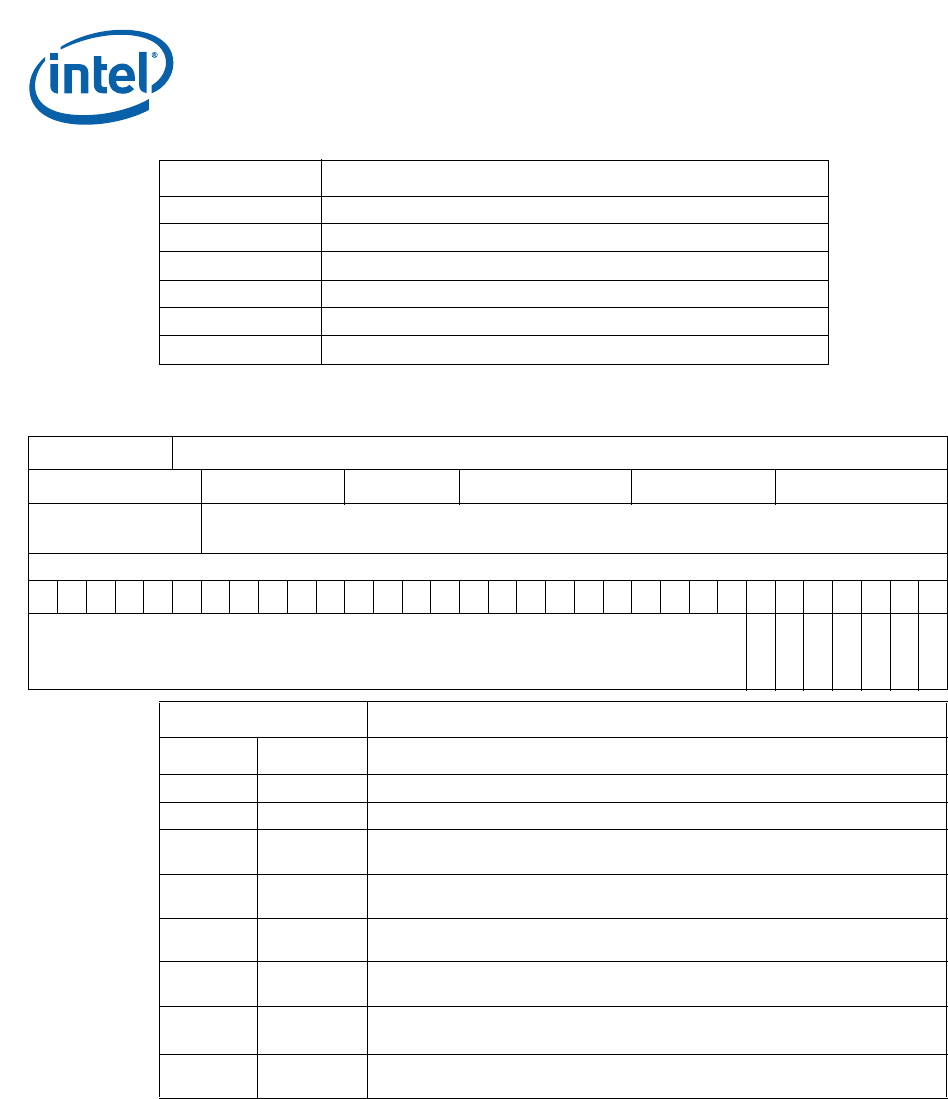

15.2.1 Transmit Control 1

0xC800 90F4 Unicast Address 2

0xC800 90F8 Unicast Address 3

0xC800 90FC Unicast Address 4

0xC800 9100 Unicast Address 5

0xC800 9104 Unicast Address 6

0xC800 91FC Core Control

Register Name: txctrl1

Hex Offset Address: 0xC8009000 Reset Hex Value: 0x00000000

Register

Description:

Transmit Control Register One

Access: Read/Write.

31 76543210

(Reserved)

MII CFG

2PRT DEF

APP FCS

PAD EN

RET EN

HALFDUP

TX EN

Register txctrl1

Bits Name Description

31:7 (Reserved)

6 MII config 0 = Configures the PHY interface as a MII.

5

Two-part

deferral

1 = Causes the optional two part deferral to be used.

4Append FCS

1 = Causes FCS to be computed and appended to transmit frames before they

are sent to the PHY.

3 Pad enable

1 = Causes transmit frames less than to minimum frame size to be padded

before they are sent to the PHY.

2 Retry enable

1 = Causes transmit frames to be retried until the maximum retry limit shown in

the Transmit Control 2 Register is reached, when collisions occur.

1Half duplex

1 = Half-duplex operation

0 = Full-duplex

0

Transmit

enable

1 = Causes transmission to be enabled.

Address Description