Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 455

High-Speed Serial Interfaces—Intel

®

IXP42X product line and IXC1100 control plane

processors

There is one register titled the HSS Clock Divider Register that provides a means to

generate a unique data clock for each of the two IXP42X product line and IXC1100

control plane processors’ HSS interfaces. This may help reduce BOM cost by eliminating

the need for a clock oscillator in cases where the system can tolerate an imperfect data

clock with a certain amount of jitter. The IxHssAcc API will configure the HSS clock

divider register with the appropriate values depending on which clock frequencies is

selected, being 512 KHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, 4.096 MHz, and 8.192

MHz. This is discussed further in the next section:

17.5.1 HSS Clock and Jitter

Each of the two High-Speed Serial (HSS) interfaces — on the IXP425, IXP423 and

IXP421 network processors — can be configured to generate an output clock on the

HSS_TXCLK and HSS_RXCLK pins. This output clock, however, is not as accurate and

stable as using an external oscillator. That is because the HSS clock is based on the

internal, 133.32-MHz AHB bus. This frequency does not divide down easily.

Subsequently, jitter and error are introduced into the resultant HSS output clock.

If developers are clocking a framer, DAA, or other device with a sensitive input PLL,

they should use an external clock.

To provide developers with additional data, this chapter contains five tables:

1. Table 155, “HSS Tx/Rx Clock Output” on page 455

2. Table 156, “HSS Tx/Rx Clock Output Frequencies and PPM Error” on page 456

3. Table 157, “HSS Tx/Rx Clock Output Frequencies And Their Associated Jitter

Characterization” on page 456

4. Table 158, “HSS Frame Output Characterization” on page 456

5. Table 159, “Jitter Definitions” on page 457

The jitter and error calculations, in the following tables, are valid only for IXP400

software Release 1.4 and later.

17.5.2 Overview of HSS Clock Configuration

The HSS clock is generated by the WAN/Voice network processor engine (NPE). This

clock can be configured by using the HSS API in IXP400 software releases 1.4 and later.

The clock speed can be set by using the HSS API.

It is important to be aware of the jitter and frequency error on the output clock of the

HSS. The six clock values in Table 155 have been pre-defined by IXP400 software

release 1.4 to minimize jitter and PPM error. The values shown in the following table are

those currently supported in software.

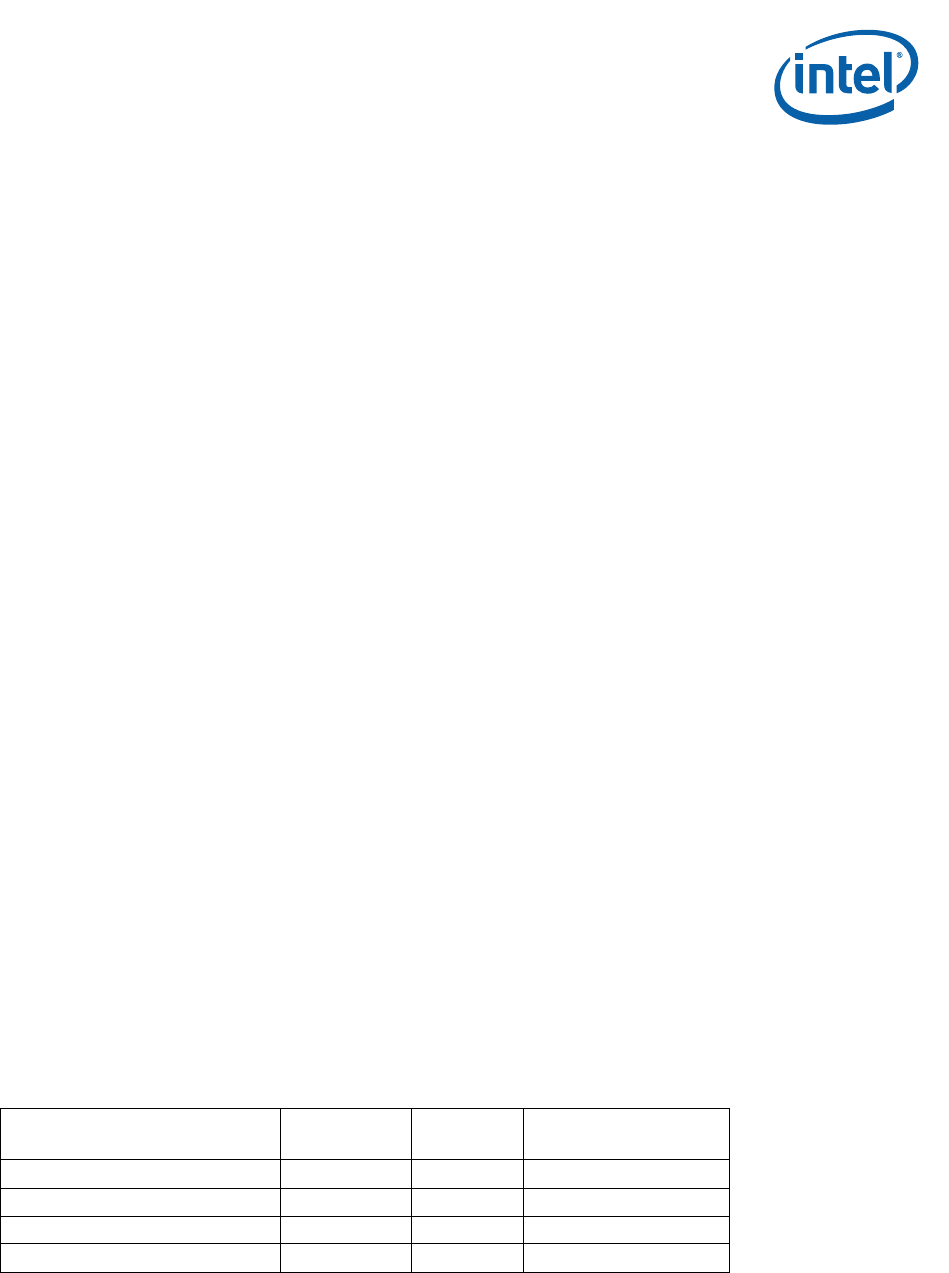

Table 155. HSS Tx/Rx Clock Output

HSS Clock Output Frequency Protocol

Frame Size

(Bits)

Notes

512 KHz GCI 32 1

1.536 MHz GCI 96 1

1.544 MHz 1 T1 193

2.048 MHz 1 T1/E1 256 2